- 易迪拓培训,专注于微波、射频、天线设计工程师的培养

数字电路中的电源电压波动和源阻抗

录入:edatop.com 点击:

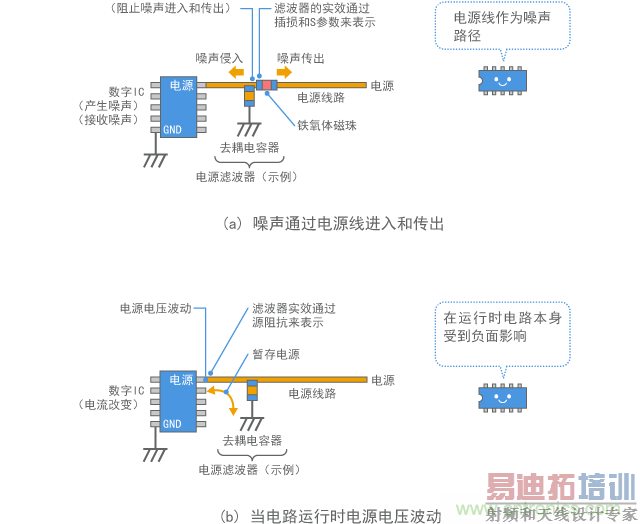

同时,电源为负载电路提供电流。如图2(b)所示连接一个数字IC,数字IC会通过其运行改变电源电流,使电源感应到噪声,进而可能干扰电路本身的运行。下文中将这一现象称为电源电压的波动。电源滤波器也需要具有抑制电源电压波动的作用。

一般而言,滤波器防止噪声传导的效果与抑制电源电压波动的效果并不不同。其抑制电源电压波动的效果通过源阻抗来表示。当电源电压的波动传到外部时,噪声将会如图2(a)所示被传出。尽管这两种噪声看似不同,但它们却相互关联。

本章节主要针对数字电路,介绍电源电压波动和源阻抗。

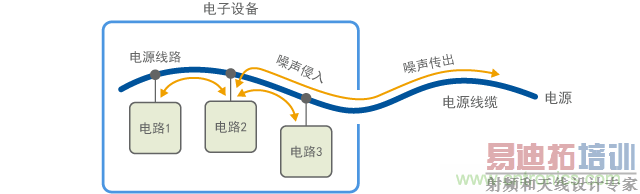

图1 噪声经过电源线的出入口

图2 电源噪声抑制的两种视角

电源电压波动

(1) 数字电路的运行与源阻抗

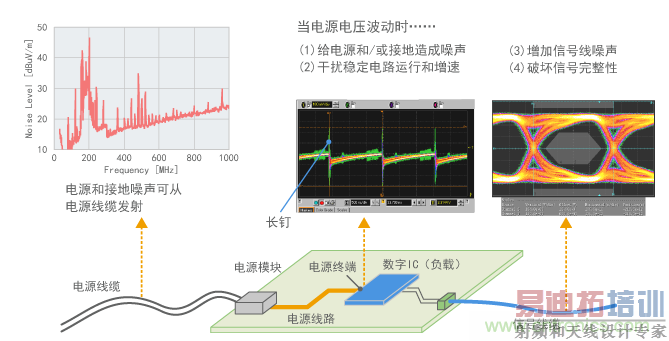

如第2章的章节2-3所述,在电路运行中,数字电路的电源和接地中会产生长钉形的电流。这种电流将噪声感应到电源,使电源电压发生波动,导致电路无法稳定运行。它也会更容易引起信号波形和产生噪声方面的问题。

防止电源电压波动的功能通过源阻抗[参考文献 5]来表示。源阻抗是电源品质的一个指标,表示为图2(b)中连接数字IC(负载)的位置处(电源端子等)电源侧的阻抗。 [p]

(2) 电源电压波动的影响

图3中的示意图解释了当噪声被感应到数字IC电源时整个设备的噪声产生的影响。IC电源电压波形如图中间所示。根据长钉形的波形,可以发现 这是数字电路运行中感应的噪声。在此,长钉形的波形被称为电源电压的波动。这种效应会干扰电路的稳定运行和增速,或将噪声扩散至电源线或信号线,或使信号 波形失真,如图中(1)到(4)所示。如果扩散至电源线的噪声由电缆发射,则会成为关乎噪声规定的问题。

图3 电源电压波动的影响

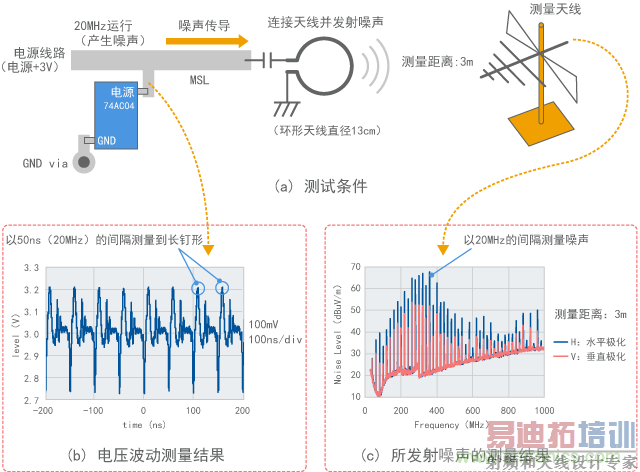

(3) 电源噪声的频谱

电源电压的波动源自在数字信号上升和下降瞬间流经的电流。因此,如果噪声源的电路很简单,电源电压波动相关的噪声也具有像信号谐波一样的离散分布频 谱。图4给出了一个实验的示例,其中以20MHz运行的数字IC的电源发射噪声。电源电压每隔50ns(20MHz)呈现出长钉形,而且可以发现 当噪声发射时,每隔20MHz就可以观察到噪声频谱。

图4 观察数字IC电源噪声的实验

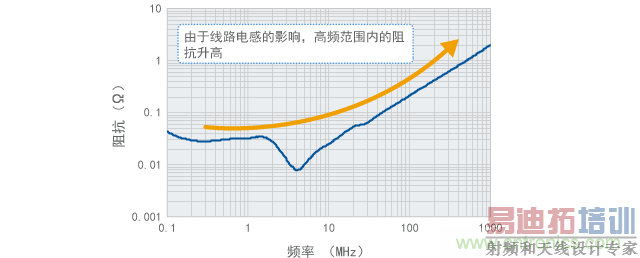

(4) 源阻抗的频率特征

为减少电源电压波动,要降低源阻抗。因为根据欧姆定律阻抗与电压存在比例关系,如果流经数字IC的电流恒定,电压波动就会减少,因为源阻抗也降低了。

图5给出了源阻抗测量结果的一个示例。一般而言,电源具有较小的源阻抗更好,这样能提供较高的电源性能和出色的降噪能力。

图5 源阻抗测量结果的示例

(5) 源阻抗测量

因为源阻抗非常小,所以很难进行测量。图5显示了通过网络分析仪测量的结果。由于测量值随测量探针的位置而改变,因此需要在既定的位置仔细 进行测量。通常是在IC(负载)的电源端子和接地端子之间测量。为消除IC的影响并提高测量精确性,需要暂时将IC从PCB移开,然后测量PCB侧的阻 抗。 [p]

去耦电容器

如果电源电路基于负载的电流恰当运行,源阻抗的理想值应该为零。但是,在现实生活中,在10MHz以上的高频范围内阻抗会逐渐增加(如图5所示),而且在某些情况下,它还会高达几10Ω。

(1) 去耦电容器

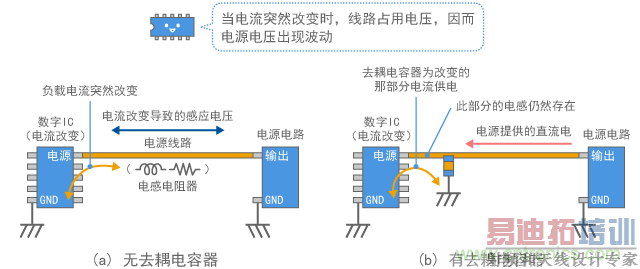

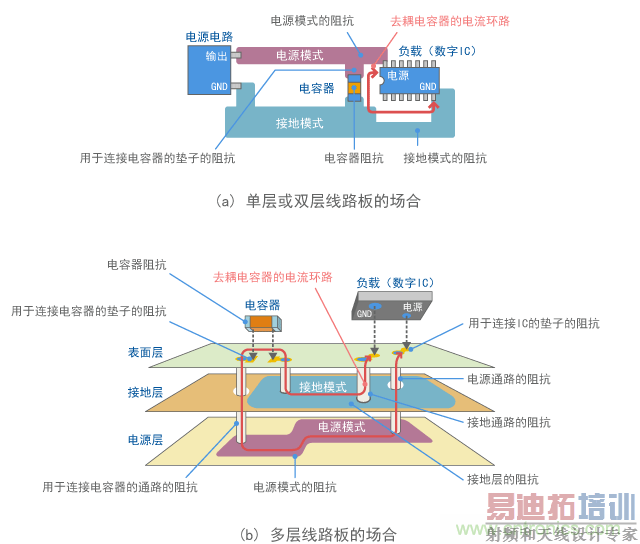

如图6(a)所示,由于连接电源和负载的线路具有电感和电阻,即使电源在理想情况下运行(0Ω),负载侧还是会产生一些阻抗。特别是在高频范围内,线路中的电感是使阻抗升高的主要原因。

为降低高频范围内的源阻抗,如图6(b)所示在电源和地线之间靠近负载的地方连接一个电容器。这个电容器称为去耦电容器、电源旁通电容器或者旁通电容器等。

图6 去耦电容器的运行

(2) 电源电压波动的吸收

去耦电容器作为临时储电器吸收负载电流的改变,防止电源电压的波动和噪声的产生。因为其放置在负载附近,线路阻抗造成的影响会减少。从阻抗的角度而言,这种运行方式意味着源阻抗降低了。

但是,即使使用了去耦电容器,还是存在一段导线(如图6(b)所示),并产生电感。因此,布置电容器时,应使这部分越短越好。

(3) 噪声限制效果

从噪声抑制的角度来看,可以认为去耦电容器限制了负载和去耦电容器之间线路部分负载侧电源产生的高频电流,从而防止了噪声传到电源线更远的地方。因 此,去耦电容器不仅是稳定电路操作而且也是防止噪声产生的重要元件。为了更有效地防止噪声传导,可如图2(a)所示增加一个铁氧体磁珠,或者也可 使用具有出色静噪性能的电容器,如三端子电容器。

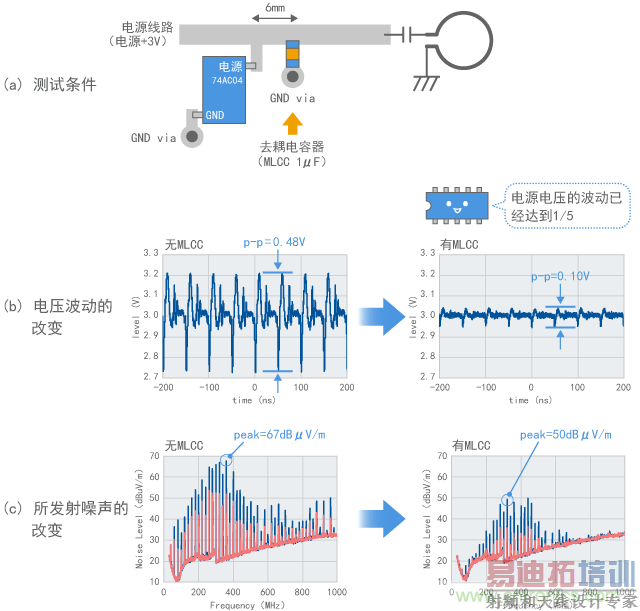

(4) 证实去耦电容器的效用

图7显示了针对图4中的测试电路使用去耦电容器时电源电压波动发生的变化。通过连接电容器,电压波动幅度从0.48V降至0.10V,同时噪声发射降低了10dB。

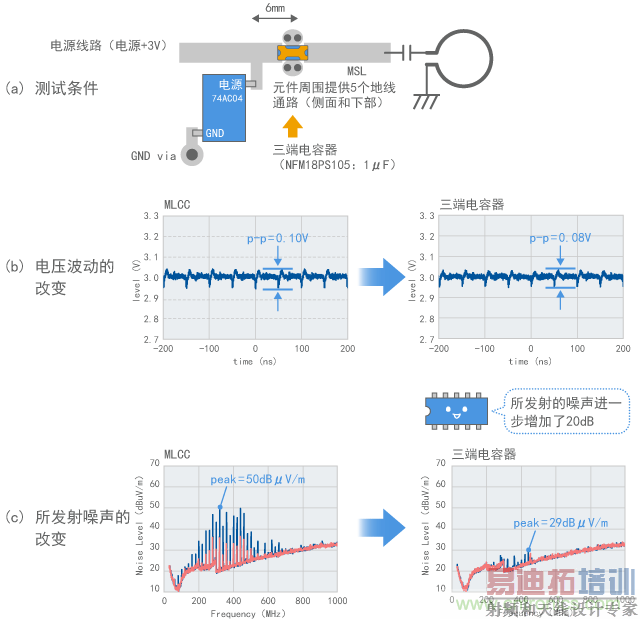

图8指出了使用更高性能的三端子电容器的情形。对比使用普通MLCC的情形,电源电压的波动幅度有所降低,同时也显著抑制了噪声发射。这是因为三端子电容器具有专为降噪设计的有利结构。三端子电容器将在第6章中进一步讲述。

图7 通过去耦电容器抑制电源电压波动

图8 当三端子电容器用作去耦电容器时

[p] 环路阻抗

(1) 源阻抗的频率范围

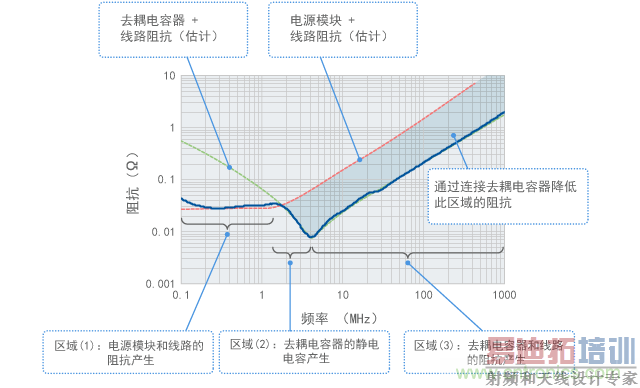

图5中所示的源阻抗实际上给出了一个例子,其通过使用多个去耦电容器实现了极低的阻抗。这些频率特征可以分为如图9所示的三个区域。

(2) 什么控制着低频范围?

①的低于1MHz较为平缓部分可观察到的电源模块输出阻抗。如果不使用去耦电容器,阻抗会从图中虚线所指示的较低频率处开始增加。这是因为电源模块的输出特征和线路中电感的作用。

如果使用去耦电容器,可抑制高频范围的阻抗。

(3) 什么控制着高频范围?

图9中(2)和(3)指示的是相对较高的频率范围,在其中可观察到去耦电容器的阻抗。(2)是电容器存在电容阻抗的频率范围,可通过将静电 容量的大小进行一定程度地控制。(3)是电容器存在电感阻抗的频率范围。为进一步降低此区域的阻抗,需要降低去耦电容器的ESL,或者降低连接至电容器线 路的电感。

图9 源阻抗的频率特征及发挥作用的元件

(4) 环路阻抗

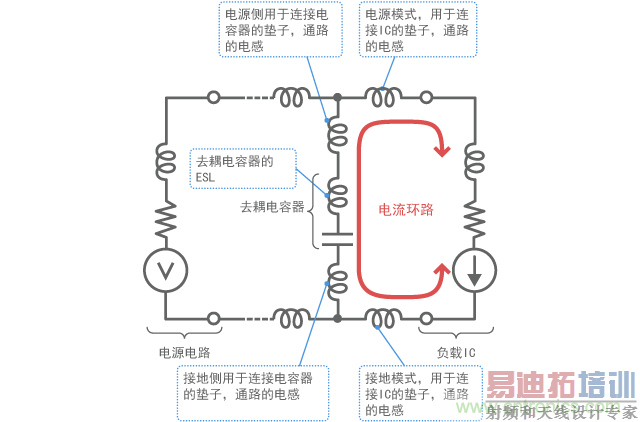

线路电感由负载IC和去耦电容器之间连接的模式和通孔构成,如图10中所示。将经过这些元件的整个电流环路之和与电容器的ESL相加,可得出总电感。图11为等效电路。

去耦电容器所建立电流环路的阻抗可以称为环路阻抗。图9所示区域(3)的环路阻抗是主要来自线路和电容器本身的电感所致。

为降低高频范围内的环路阻抗,需要降低电感。也就是说,当环路阻抗的目标值为ZTarget (Ω),频率为ƒ(Hz),总阻抗为LLoop (H),可得出如下公式:

(公式1)

例如,如果需要将100MHz处的环路阻抗降低到1Ω或更少,总阻抗需要约为1.6nH或以下。这是一个极低的值。

(5) 环路阻抗的要素

因为实际电路可能存在导线分支的情况或者有多个电容器,所以不能像图10和图11那样简单地思考问题。但是,这个模型是有用的,可以作为将环路阻抗分解为各个要素的理念。为有效地尽量降低环路阻抗,需要降低在总阻抗中占很大一部分的电感。

图10 环路阻抗的要素

图11 去耦电路的等效电路

[p] 如何尽量降低环路阻抗

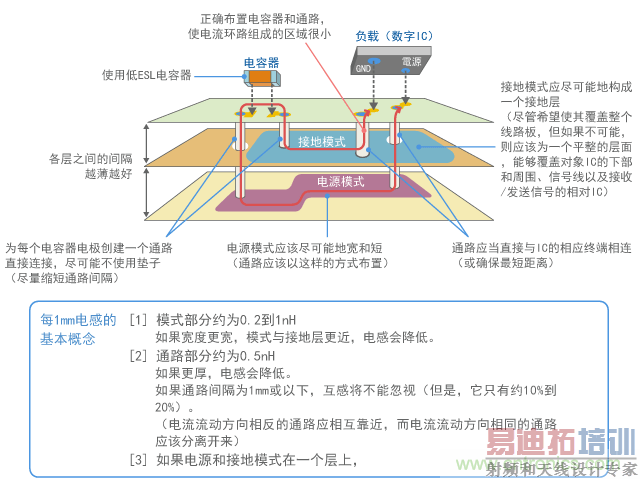

为尽量降低高频范围内的环路阻抗,需要降低电容器的ESL和线路的电感。如果能够进行巧妙地设计,可以将双层基板的总电感降低至约几nH,多层基板则可降低至1nH或以下。在图9的示例中,其值约为0.3nH。

(1) 使用低ESL电容器

每个电容器(如果是MLCC)的ESL约为0.5nH,在总电感中占很大一部分。为降低此值,可使用低ESL电容器。

(2) 降低线路电感

要降低线路和通孔中的电感,线路和通孔应该要“粗且短”。例如,在布置电容器和通孔时,应减少图10中所示电流环路的面积。此外,布局模式应该尽可能地宽。将电容器放置在(基板另一侧)IC的正下方,并使基板变薄,通常能够让电流环路变小。

(3) 电容器和通孔的并联

当并联使用众通孔通路和电容器时,可降低阻抗。

因为线路和通孔的电感非常小,而且还涉及互感,所以很难得到一个简单的判断。为此,可使用电磁模拟装置估计这样的环路阻抗。图12给出了电感的一 般范围供您参考。但是,根据线路的不同形状,电感可能相差好几倍。此外,即使只是1mm的长度,也会造成约0.5nH的电感,这是无法忽略的。

图12 降低环路阻抗的电容器布置

(4) 注意反谐振

如果使用了两个或更多个电容器,需要考虑电容器之间发生的谐振。一般而言,如果并联连接具有不同自谐振频率的多个电容器,反谐振会导致具有高阻抗的频率(将在第6章中进行探讨)。

除了线路电感之外,还需要考虑在100MHz以上的高频范围内存在的静电容量。此外,电源层的谐振和IC封装的影响也会在高频范围内变得显著。鉴于要素如此复杂,也可使用电磁模拟装置。

[p] 源阻抗和噪声抑制之间的不同

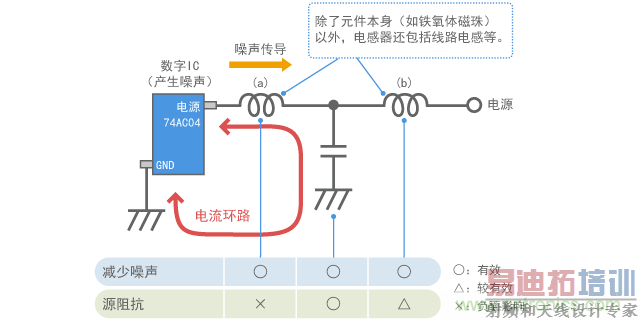

前已述及,使用电源滤波器的另一个重要目的在于防止噪声进入和传出。通常而言,滤波器包括电容器和电感器,它们形成一个低通滤波器。图2(b)显示了电源用典型滤波器的结构。(滤波器的功能和结构将在第3章中进一步描述。)

尽管电容器和电感器都能减少噪声,但它们在抑制源阻抗方面以不同的方式发挥作用。图13显示了一个T型滤波器的情形,其中电容器用于降低阻抗,而 电感器却用于增加阻抗。因此,在使用电容器时,如果使用的是如图7和8所示的高性能电容器,通常能在抑制电源电压波动和减少发射的噪声方 面取得更好的成效。但是,如果使用电感器,就需要注意,即使能够减少噪声,但却可能加剧电源电压的波动。因此,如果使用电感器抑制IC电源终端的噪声,应 该将电感器放置在图13(a)中的位置(b)而不是位置(a)。此外,耦合电容器静电容易应该要足够大。

图13 使用滤波器元件的作用和反作用

在噪声路径上采取噪声措施

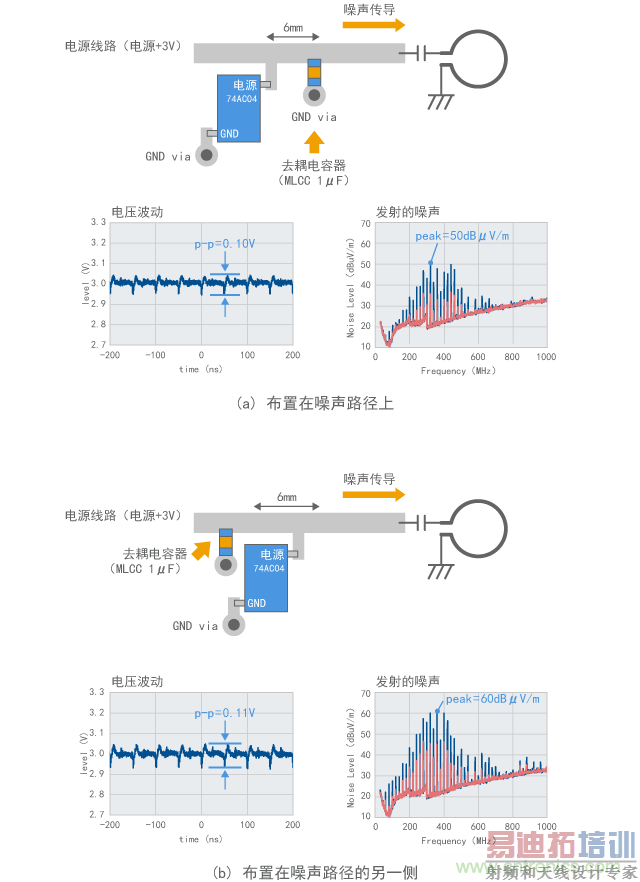

尽管使用去耦电容器降低了源阻抗从而抑制了电压波动,但在减少噪声方面可能无法看到充分的实效。图14给出了一个模拟之前测试中相关情形的示例。

图14中指示了电容器(a)和(b)的位置((a)与图7中采用MLCC的一样)。两个IC都在距电源终端6mm的位置处布置了去耦电容器,因此可以认为环路阻抗是相同的。电源电压波动也在同样的范围内。但是,(b)发射的噪声比(a)高10dB。

产生这种差别的原因在于(a)在能够传导噪声的路径上使用电容器,而(b)在(IC和会发射噪声的天线之间的)噪声路径之外使用电容器。因此,需要沿着噪声路径连接滤波器,以便消除噪声。 [p]

图14 在不同位置连接电容器产生的噪声抑制效果的差别

噪声路径未知时怎么办

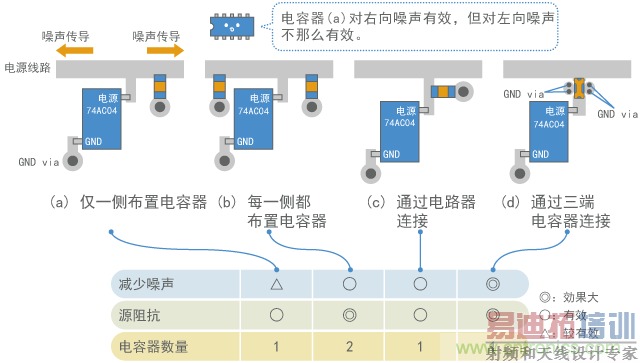

图14中的测试说明,如果提前知道噪声路径在哪里,就可以很轻松地将电容器连接在位置(a)。但是,噪声路径通常是未知的。在某些情况下,线路的两个部分都存在噪声路径,如图15(a)所示。这时,哪里才是放置电容器的最佳位置呢?

在这种情况下,可如图15(b)所示将电容器放置在线路的两侧以限制噪声。尽管这种方法需要更多的电容器,但由于电容器是并联连接在线路左侧和右侧,可以减少噪声干扰的风险,同时也可降低环路阻抗。

或者,可如图15(c)所示通过电容器再连接电源线。这种方法可以加强源阻抗和降噪效果,但不足以完全消除噪声。

效果最好的方法是通过一个低ESL电容器(如三端子电容器)连接电源线,如图15(d)所示。这样可以获得源阻抗和噪声均减少的出色效果。

图15 噪声传到两侧时的电容器布置

如果针对多层电路板使用电源层,由于其线路电感小,因此有利于抑制源阻抗。但是,直接连接电源终端和电源层会导致难以缩小噪声传播路径的宽度,从而 不利于防止噪声传出。图15(c)和图15(d)所示的通过电容器连接噪声源电源(电源层)的方法也适用于多层线路板,能够改善噪声抑制 效果。

EMC电磁兼容设计培训套装,视频教程,让您系统学习EMC知识...