- 易迪拓培训,专注于微波、射频、天线设计工程师的培养

利用FPGA实现工业以太网交换机设计优化

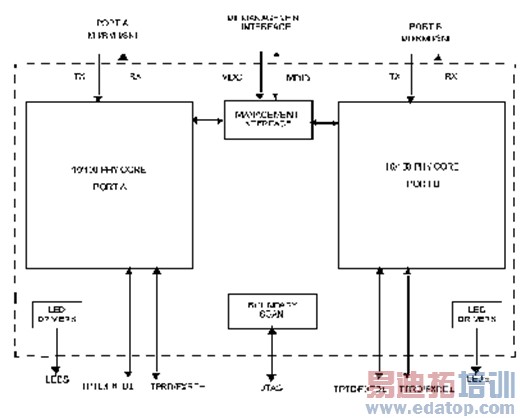

在该设计中,Nios II嵌入式处理器支持交换机的IP配置和管理,并能运行用户数据报协议(UDP)栈、IEEE 1588协议栈和精确的时序同步,并支持双路10/100 PHY收发器的PHY管理和线路诊断功能(如图4所示)。

嵌入式处理器还可用于高层组网功能,如运行生成树和快速生成树算法以及终结TCP/IP链接。生成树协议 (STP)和快速生成树协议(RSTP)是链路管理协议,它们支持路径冗余,可防止网络内出现不需要的环路(要使工业以太网络正常工作,两个节点间只能有一条有效路径)。

PHY收发器

图5:美国国家半导体公司的PHY收发器框图。

每个收发器都有两个完全独立的10/100Mbps端口供多端口应用使用,如图5所示。该收发器的端口切换还允许两个端口经配置提供完全集成的范围扩展、介质转换、基于硬件的快达ns级的故障切换(fail-over)以及端口监测功能。

该器件整合了用于公共工业以太网拓扑的多端口支持。特别是设计师要获得对不同应用的冗余支持,需要具备在各种条件下处理故障切换的能力。从一个网络栈切换到另一个网络栈需要不短于几百毫秒的时间,但一些应用(如安全应用)需要极其迅速地、最好是在PHY层实现的故障切换。该参考设计内的收发器从一个端口切换至另一个端口的时间是ns级,即使主机仍管理着控制路径。收发器信号路径中的架构改进使性能远远超过了最低PHY层规范要求,完全可以解决抖动和延时等设计问题。每个以太网PHY层由一个参考时钟驱动。为了尽量减小抖动,PHY层规范要求采用极其精确的时钟,其精度要在收发器25MHz参考时钟的50PPM以内。另外,为了满足规范要求,起始抖动必须非常小。为了解决这个问题,架构内整合了一个容忍更大抖动的机制。器件架构还针对实时以太网操作优化了延时性能,以确保把交换机延时降至最小。

作者:Francois Balay 来源:电子工程专辑

上一篇:三层交换机的智能流处理技术

下一篇:建设安全的交换机系统