- 易迪拓培训,专注于微波、射频、天线设计工程师的培养

利用FPGA实现工业以太网交换机设计优化

录入:edatop.com 点击:

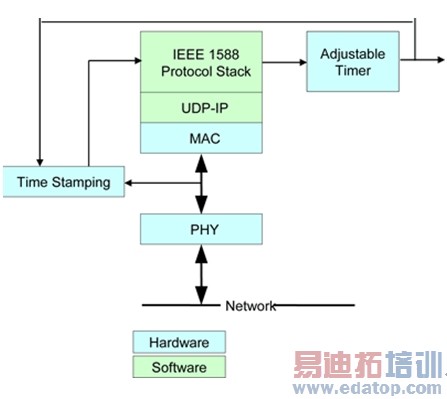

为实现边界时钟应用,交换机设计同时实现了IEEE 1588 V1主应用和从应用。

与主机通信的端口被自动配置为从端口。嵌入式1588应用程序经从端口生成一个精确时钟,并将该时钟信息前转送到被自动配置为主端口的其它端口。

与可编程定时器的紧密整合确保了该时钟与主时钟的同步精度在100ns以内。

在交换机内,每端口可最多实现两个按优先级排列的队列,以便为关键服务提供服务质量(QoS)保证。交换机还能通过编程并利用3位VLAN优先级字段、6位 DiffServ第三层代码点(IPv4)或8位服务类别(IPv6)对流量进行识别和分配优先级。

交换机设计支持IEEE 1588版本1边界和版本2透明时钟应用。可对该设计作进一步修改和强化以增加定制逻辑,例如在传统协议或PCI等不同系统接口上增加桥接应用软件,从而方便将交换机集成进现有系统。

图4:包括软件和硬件在内的IEEE 1588框图。

作者:Francois Balay 来源:电子工程专辑

上一篇:三层交换机的智能流处理技术

下一篇:建设安全的交换机系统