- 易迪拓培训,专注于微波、射频、天线设计工程师的培养

800 Mb/s高速解调器的定时恢复算法及实现研究

1 引 言

跟踪与数据中继卫星系统(TDRSS)是在航天技术领域实现天地一体化综合信息网的重要组成部分,他在军事战略、战术和民用方面均具有重要地位和广阔的发展前景。就其高速数据传输业务来讲,天上中、低轨道用户航天器和数据中继同步卫星与地面上终端站构成一个实时的、宽带的大地数据传输链,其数据速率从40 Mb/s到几再Mb/s,甚至将来更高的Gb/s水平。这就需要一个高速数据的宽带传输的调制解调信道。

在数字接收系统中,为了正确恢复出发送端的符号信息,必须做到定时同步。定时同步恢复技术是无线通信的关键技术之一,对接收机的整体性能有直接影响。定时误差的提取方法有很多,大体可以分为两种:数据辅助(DA)和非数据辅助(NDA)。在高速数传系统中,一般都采用的是非数据辅助算法,他具有快速捕获定时误差的优点,而且不需要插入额外的定时信息,增加了实际传输数据信息速率。

针对800 Mb/s 8PSK高速调制信号,本文采用MartinOer-der包络平方DFT定时恢复算法,并通过仿真和FPGA实现验证了其有效性。

2 定时恢复算法及实现

2.1 定时相位误差的影响

当高速数传系统存在定时相位偏差时,ADC模块对输入信号进行定时采样的时刻将会偏离期望的最大信噪比采样点。对于升余弦特性的匹配滤波信道,波形成型的符号峰值点就是所期望的最大信噪比采样点,这种定时采样时刻的偏离称为定时相位误差。当存在定时相位误差时,由于ADC定时采样不在符号峰值点上,一方面信号幅度的减小使得采样点数据的信噪比变差,另一方面码间干扰的增加也使得采样点数据的信噪比恶化,从而导致系统性能的信噪比实现损耗。这里,将符号周期划分为32等份,即将定时相位误差刻度划分为(-16,+16)范围。通过计算机仿真,对于滚降系数a=0.6的升余弦特性信道,在不同的定时相位偏差时8PSK调制解凋通道的符号误码率与输入端比特信噪比关系曲线如图1所示。

在输入比特信噪比8 dB工作点上,定时相位偏差刻度在±1,±2,±3时,其信噪比实现损耗分别为:0.4 dB,1.2 dB,2.2 dB左右。这表明当系统信噪比实现损耗要求小于0.4 dB时,则相对应地要求符号同步的定时相位偏差或者定时相位抖动小于符号周期的±3.125%(1/32)。这就是定时恢复环路实现的定时相位误差精度要求。

2.2 包络平方DFT定时恢复算法

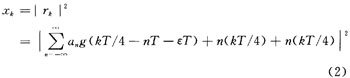

对于线性调制(如MPSK,MQAM等)的数字信号,接收机收到的等效低通信号可以表示为:

其中an是每符号能量Es的符号信息正交矢量复数表示,g(t)=gT(t)*gR(t)(*为卷积符号)是发射端与接收端合成的升余弦频率特性波形成型单位冲击响应脉冲,T是符号周期,z(t)是功率密度为N0的加性白高斯噪声(AWGN),ε(t)是未知的相对时间延迟(即定时相位误差τ=ε(t)T)。由于ε(t)是慢变化的,在定时相位误差估计时进行分段处理,而在每一段可以认为ε(t)=ε,是一常数,将这一段时间内的采样数据联合起来获得此定时相位误差估计值。

包络平方定时恢复算法先对输入复包络信号取平方(即非线性变换处理),然后通过DFT变换,提取符号周期的频率谱线,再统计地估计出其频谱矢量的相位角。对接收机匹配滤波后的信号以采样速率fs=4/T(即每符号4倍采样)进行采样,并计算其包络平方,得到的序列为:

设L符号分为一段,则通过离散傅里叶变换(DFT)可得到其第m段序列的在符号速率频谱线上的频谱分量为:

其中实部对应着偶数采样点,而虚部对应着奇数采样点。其矢量的归一化相位角为:

2.3 包络平方定时算法的FPGA实现

针对该高速数传卫星解调器的高速数据处理情况,在这里导出高速数据的定时相位误差估计的并行结构实现算法。该高速解调器的匹配滤波部分采用并行结构,并行输出4个符号,即16个采样点(ADC采样为4倍采样)。因此,例如取L=128个符号为一段进行积累运算,再将他划分为32个小段,每小段为L1=4个符号。对于8PSK正交接收信号可以表示为:

应该注意,第一种平方的和差运算实现中需要4个平方运算和2次加法运算;而第二种是变系数乘法运算,实现中需要2个双变量乘法运算和5次加法运算。在FPGA实现时,需要比较这两种方式的资源利用特点。在这里选择第一种方式实现。其特点是,可以利用单变量的ROM查表法实现平方运算,这样能够得到较好的计算精度。可见这种定时相位估计的包络平方算法很适合采用并行结构的流水线方式FPGA电路实现。

其次,定时相位误差估计算法采用符号积累方式求得其估计值,其估汁精度与符号积累长度L、输入端比特信噪比有关。因此,对于不同的输入比特信噪比,计算机仿真分析此定时相位误差估计精度(在这里以100次估计值的估计偏差均方根衡星),如图2所示。设有L=64,L=128,L=256,L=512和L=1 024五种情况,L≥256时其估计精度达到10-2量级;L≥512时其什计精度达到10-3量级。估计精度量级的选择受FPGA实现资源、系统指标的制约,也受定时恢复环路参数设计的制约,实际上102量级足够。因此该系统实现时取L=512个符号进行积累运算处理是比较恰当的,而且考虑到实际非理想信道因素后他也能满足性能要求。包络平方定时相位误差估计的高速数据并行结构算法方框图如图3所示。

3 计算机仿真结果

本文给出基于高速卫星解调器并行定时估计结构的计算机仿真结果。

计算机仿真验证表明,在输入端比特信噪比10 dB工作点上,对于不同的输入端定时相位误差,其相对定时相位误差估计值表现为以(-0.5,0.5)为线性关系,如图4所示。由此可见,定时相位误差估计值与输入端实际定时相位误差构成直线的线性控制关系。这表明包络平方定时相位误差估计算法对定时恢复的校正控制是可行的。

4 硬件电路实现

由于800 Mb/s数字序列输入到R2/3TCM卷积编码器,构成400 Msps并行3 b的8PSK符号速率信息。接收端按照每符号4个采样点对400 Msps速率的符号信息进行采样产生的信息速率为1.6 Gsps。以目前的FPGA芯片能力是无法完成这么高速率的信息处理,因此我们必须采用并行结构实现。Xilinx公司V4系列的FPGA芯片具有高速串/并功能的ISERDES硬核可以完全满足接收机I,Q两路1:8串/并的需要,这样每路信号的速率降到为50 Mb/s(ADC具有1:4的串/并功能),适合FPGA芯片工作的要求。图5为串/并功能模块时序仿真图。

定时估计主要由3个模块组成:FPGA芯片里的专用18×18位乘法器实现非线性平方器功能模块;采用普通的逻辑资源完成128次累加器的功能;采用芯片甲的专用16 kB ROM储存器实现定时偏差系数的提取,时钟进率为75 Mb/s。定时误差估计的FPGA硬件实现框图如图6所示。

5 结 语

定时同步问题是卫星解调器中的关键问题,对于8PSK高速卫星解调器系统,本文提出了包络平方定时相位误差估计算法的并行结构,实现了800 Mb/s高速数据定时相位估计。定性分析和计算机仿真结果证明了该算法结构可以高效地对定时偏差进行准确估计。

来源:电子产品世界

上一篇:基于分层方法的VoIP安全问题

下一篇:VoWLAN企业级应用模式及解决方案