- 易迪拓培训,专注于微波、射频、天线设计工程师的培养

基于DSP的语音降噪系统设计

在现实的语音通信中会不可避免地受到来自环境中的背景噪声影响,致使通信质量严重下降,甚至听不清楚对方讲话的内容,因此对带噪语音信号进行降噪已经成为语音通信中的一个非常迫切的课题。近年来,随着VLSI技术的发展和高速DSP芯片的出现,语音增强方法走向实用化[1]。本文所介绍的语音降噪系统能够有效地实现数字降噪功能,由于降噪处理时不但要进行信号的采集与回放,还要进行降噪算法的实时处理,采用具有高速实时处理能力的DSP TMS320VC5509进行处理,能够满足日常生活中语音通信中的降噪要求。

1 降噪系统设计

1.1 硬件系统结构图

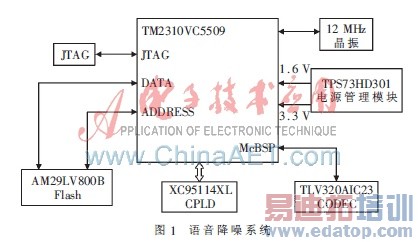

本系统采用TI公司的TMS320VC5509芯片进行信号处理和谱相减算法的处理,语音降噪系统如图1所示。系统采用12 MHz的晶振为DSP提供时钟,DSP内部工作时钟采用PLL方式设置成16倍频,使DSP的内部时钟达到192 MHz。语音采集与回放模块采用TLV320AIC23语音编解码芯片。CPLD XC95114提供读写Flash AM29LV800B和配置,启动语音编解码模块AIC23的控制信号。供电模块采用TPS73HD301,分别提供DSP芯片所需的1.6 V内核电压和3.3 V的I/O电压。

1.2 主要电路原理分析

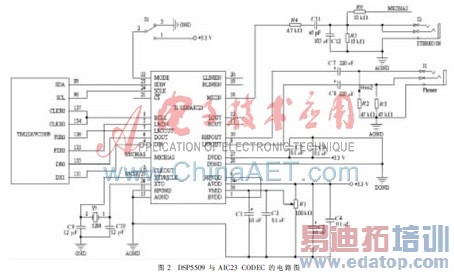

图2为5509DSP与TLV320AIC23的接口原理图。

音频Codec芯片TLV320AIC23通过外围器件对其内部寄存器进行编程配置,使用灵活,其配置接口支持SPI总线接口和I2C总线接口, 数据传输格式支持右判断模式、左判断模式、I2S 模式和DSP模式4种方式,其中TI 模式专门针对TI DSP设计[2,3]。C5509的多通道缓冲串口MCBSP可以配置为SPI总线接口,其串行数据传输格式与TLV320AIC23的DSP模式兼容,此外,这两款芯片的I/O电压兼容,从而使得C5509与TLV320AIC23可以无缝连接,系统设计简单。

MODE引脚作为串行接口输入模式选择端,0为I2C模式,1为SPI模式;由于C5509片内外设含有I2C模块,直接使用C5509的I2C模块控制TLV320AIC23,此时C5509作为I2C总线的主设备,TLV320AIC23作为从设备,通过编程完成对TLV320AIC23的配置。

TLV320AIC23的数字音频接口采用DSP模式,将TLV320AIC23配置为主设备。与DSP的McBSP0无缝连接,将其作为双向的数据收发通道。输入输出的帧同步信号LRCIN、LRCOUT分别接McBSP串口的FSX0与FSR0,时钟信号BCLK与McBSP的串口输出时钟CLKX0相连,同时通过CLKX0驱动输入串行时钟CLKR0,以保证串口数据收发的一致与同步。SCL和SDI分别是 TLV320AIC23的控制端口和数据输入端,分别和C5509的I2C模块端口 SCL和 SDA 相连。

1.3 音频信号的采集与回放

此系统中采用MICPHONE采集语音信号,把采集的语音信号经过模数变换,进入DSP后再经过滤波存储到DSP的片内存储空间。然后调用谱相减算法降噪软件进行降噪处理,得到新的处理后的数据再经过数模变换,放大后从耳机输出。

通过MIC采集的语音信号通过TLV320AIC23语音编解码芯片对语音进行模数转换。TLV320AIC23是一个高性能的多媒体数字信号编解码器,该模块具有模数转换器、数模转换器,使用了高效的 Multibit sigma-delta 和过采样数字插补滤波技术,支持 16、20、24 和 32位格式从8 kHz~96 kHz采样频率的音频信号的采集与回放,并具有较高的信噪比(SNR)和较低的能耗。利用多通道缓冲串口McBSP(multiply—channel buffer interferce)与DSP通信。把通过TLV320AIC23模数转换后的数据通过McBSP1传送给DSP进行降噪处理,处理后的数据经过数模转化后传送到耳机输出。

2 系统算法与软件设计

2.1 谱相减算法[4,5]

目前降噪算法具有代表性的有自相关算法、自适应噪声滤波法、短时谱幅度估计法、谱相减算法、小波变换等。谱相减算法因具有运算量小、容易实时实现、增强效果好等特点,是目前在降噪系统中最常用的算法之一。

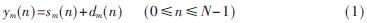

谱相减算法的基本原理是在频域将噪声的频谱分量从带噪语音信号的频谱中减去。谱减的提出前提是假设语音信号与加性噪声相互独立,它假设噪声是统计平稳的,即有语音期间噪声振幅谱的期望值与无语音间隙噪声的振幅谱的期望值相等,用无语音期间测得的噪声频谱的估计值取代有语音期间的噪声频谱,与含有噪音的语音频谱相减,即可得到语音频谱估计值。假设带噪语音的模型表达式如式(1):

其中sm(n)表示纯净的语音,dm(n)表示噪声,ym(n)表示带噪语音。其中m=0,1,2,…,M-1;n=0,1,2,…,N-1;M、N分别表示一段语音中包含的帧数和每帧信号的长度。

在实际中由于语音信号是不平稳的,但是具有短时平稳性,因此计算时通常要加窗处理。设Yk、Sk、dk分别表示带噪语音,纯净语音和噪声的傅里叶系数。对(1)式进行傅里叶变换,由于假设的语音与噪音是不相关的,可得式(2),即

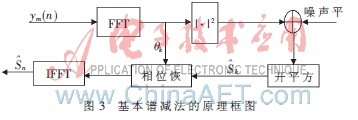

谱相减算法原理图如图3所示

2.2 系统软件设计

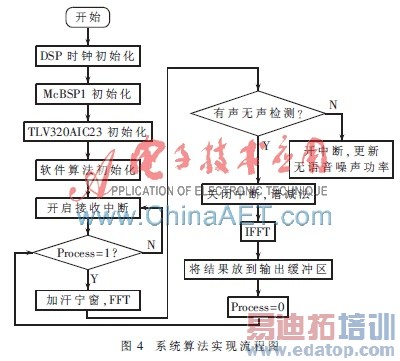

在本系统的软件设计中,软件系统主要包括主程序、中断服务程序、中断向量表和链接命令文件,其中最重要的是主程序和中断服务程序,中断服务程序主要功能是实现数据采集与数据更新。

系统主函数是程序执行的入口并完成需要的初始化工作。主函数中主要包括对时钟、多通道缓冲串口McBSP1以及对AIC23的初始化配置。接着启动串口进行正常工作,最后进行谱相减法降噪算法处理,输出降噪后的语音信号。

在该系统中,音频信号通过MIC被采集,然后经过TLV320AIC23语音编解码模块,把采集的语音信号进行信号保持、采样、量化后转换成数字信号,转换成的数字语音信号以中断方式被DSP读取,通过DSP的多通道缓冲串口McBSP1以数据帧的方式把数据存储到片上缓冲区里。当一帧数据采集完后,中断返回到主程序对数据的进行加窗处理、FFT变换,然后再进行有声无声检测,判断是否需要进行降噪处理。处理后的数据通过McBSP1输出到TLV320AIC23进行回放。软件处理流程结构如图4所示。

CPU在相应接收中断服务程序后,在服务程序中将128个采样值拷贝到处理缓冲区中等待处理,实现缓冲区的数据转换,然后置1使程序进入主程序中进行降噪处理。

本系统中实时设计中的关键技术有加窗处理、帧间重叠、帧移位、快速傅里叶变换(FFT)、快速傅里叶反变换、定点数与浮点数的转化。在进行FFT变换的时候必然会产生大量的数据,所以在对数据进行读取与存储时不可避免地要造成流水线冲突,为了解决这样的问题,可以在产生流水线冲突的两条指令间加上三个NOP指令[6,7]。

通过谱相减算法在DSP开发板上搭建的语音降噪系统中进行降噪实验,实验结果表明,本系统能够有效地降低环境噪声对语音的影响,能够有效地提高信噪比,改善语音通信质量,达到降低语音通信中的背景噪声的目的。

参考文献

[1] 黄苏雨,梁声灼,黄苏园.语音增强方法综述[J].计算机与现代化,2007,23(3):16-20.

[2] 汪春梅,孙红波.TMS320C5000系列DSP系统设计与开发实例[M].北京:电子工业出版社,2004.

[3] 丁祥,余小清.音频编解码器TLV320AIC23及其与DSP接口设计[J].单片机与嵌入式系统,2002,2(6):35-37.

[4] 王欣,罗代升,王正勇.基于改进谱减算法的语音增强研究[J].成都信息工程学院学报,2007,22(2):201-204.

[5] 张俊.基于谱减算法语音增强的研究[J].信息技术,2009,33(3):74-76.

[6] Texas Instruments.TLV320AIC23B stereo audio CODEC datamanual[Z],2003.

[7] 北京瑞泰创新科技有限责任公司. ICETEK-VCS5509 EVM用户使用手册V1.0[Z],2004.

作者:王龙 官洪运 刘捷 来源:电子技术应用

上一篇:RS通信编码器的优化设计及FPGA实现

下一篇:机顶盒中智能卡通信的实现