- 易迪拓培训,专注于微波、射频、天线设计工程师的培养

基于Nios II系统的1553B总线网络存储器设计

本文设计了1553B总线上的网络存储器。整个系统基于NIOS II内核设计,利用SoPC技术将接口部分的逻辑控制全部集成于FPGA片内,系统的存储量、结点数量均可扩展。

20世纪70年代诞生的1553B总线,是一种主从式多余度总线,对总线硬件有严格的规定,可靠性和实时性好,已经成为当今军用电子总线的首选。类似于以太网,1553B组网中也有"网络硬盘"这样的存储需求,来减轻本地的存储压力,并可作为数据中继供其他部分甚至其他组网使用。

Nios II嵌入式处理器是Altera公司于2004年6月推出的第二代用于可编程逻辑器件的可配置的软核处理器,性能超过200 DMIPS。Nios II是基于哈佛结构的RISC通用嵌入式处理器软核,能与用户逻辑相结合,编程至Altera的FPGA中。处理器具有32位指令集,32位数据通道和可配置的指令以及数据缓冲。它特别为可编程逻辑进行了优化设计,也为可编程单芯片系统(SoPC)设计了一套综合解决方案。

系统总体方案

本系统的主要功能为接收1553B网络发来的命令、数据,管理后级存储器,提供一个访 问存储器的网络接口。系统的存储器接口作为1553B总线中的从结点,平时处于待机状态,当总线上有读写命令发来时,总线转换接口根据命令从后级存储器读取数据或向其写入数据。对于总线协议,最方便的是使用现成的协议芯片,但这样做的成本非常高,1553B协议芯片的单片价格在6000元以上,这对于普通应用来说是一个不小的负担,如果能使用FPGA进行协议管理,将使成本大大降低,另外,Quartus内包含有很多存储器管理的IP核可供使用,对于1553B的协议则需要自行定制组件。

系统程序为两部分,一部分为接受网络命令及数据,另一部分为存储器的读写。在NIOS IDE环境中,使用C语言作为编程语言。

系统硬件设计

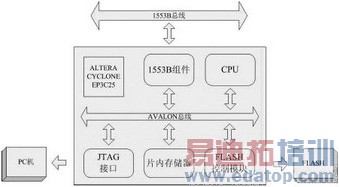

系统的硬件模块框图见图1所示。

图1 系统硬件结构框图

系统的核心芯片采用Altera公司的CYCLONE III系列FPGA EP3C25F324。它采用了65nm低功耗工艺技术进行生产,其集成度及性能有了明显地提高,但功耗却非常低,加上CYCLONE系列一直定位于低成本器件,芯片整体的性价比很高。

通过Quartus II 7.2集成的SOPC软件向FPGA内部移植Nios II内核,所需组件如下。

CPU:选用标准型CPU核,Debugger为Level 1,在满足需求的情况下尽量节约片内资源的使用。

System_ID:下载时系统认证时使用。

Jtag_uart:FPGA与PC的通信接口,NIOS IDE软件中使用会很方便。

onchip_memory:片内存储器,中转数据时使用。

FLASH:Quartus软件内部集成

有Intel公司生产的128P308的控制组件,便于开发,若需要更大量的存储,加大FLASH容量即可,如果有需要,可多挂几片。

FLASH_Bus:FLASH的数据是三态的,需要在CPU和FLASH之间加入Avalon三态总线桥。

1553B接口组件:与外部1553B总线通信的接口,Quartus软件内部未集成有该组件,需要自行开发。

在1553B的网络上,本系统是作为从结点设计的。在系统内部,1553B的接口组件需要作为Alavon总线上的主端口,其余存储器控制模块作为从端口。由于其余的端口在Quartus软件内部均有集成,所以,系统软件设计的主要工作量就是1553B接口的组件开发。

存储芯片采用Intel公司生产的128P308的FLASH芯片,符合通用接口标准,便于后续功能容量的更新升级。

系统软件设计

定制1553B组件的核心任务就是将1553B的总线信号转换到NIOS II内部的Avalon总线上。

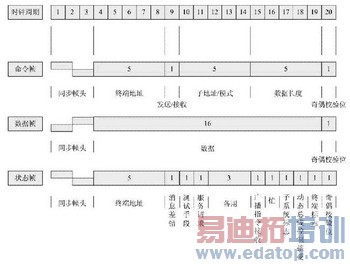

1553B组件作为Avalon总线上的主端口,选用的信号有clk、address、read、write、data、irq、reset、irqnumber等。传输方式为基本的主端口读传输和写传输。产生这些信号就需要从1553B总线上读取的帧信号来实现。1553B总线上共有三种帧,命令帧、状态帧和数据帧。这三种帧的结构如图2所示。

图2 1553B总线的三种帧结构

对于这三种帧,命令帧、数据帧和状态帧可以使用同一个缓存,因为作为存储的从结点不会主动向主结点发送数据,整个工作都是被动接收主结点的命令,等待主结点读取或写入数据,系统只有单一的状态,不会出现冲突。

对于Avalon总线中的信号,对应于帧内信号关系如下。

read/write信号:命令帧内的发送/接收位。

address信号:命令帧内的子地址以及数据长度位。

data信号:数据帧内的数据位。

irq信号:状态帧内的标志位引起。

irqnumber信号:状态帧内的具体位置。

1553B组件的API函数包括有:

altera_avalon_1553B_init()

altera_avalon_1553B_enable()

altera_avalon_1553B_disable()

altera_avalon_1553B_getframe()

altera_avalon_1553B_sendframe()

其余定制组件的步骤不再赘述。将组件通过SoPC定义完成后,命名为1553B,添加至NIOS II内核中。

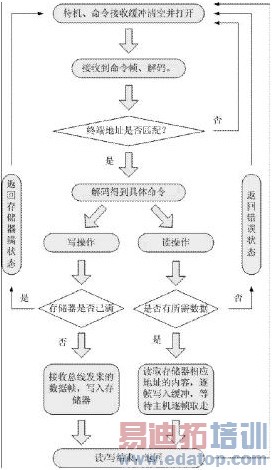

FPGA内部的工作流程如图3所示。

图3 FPGA内部工作流程

系统平时处于待机状态,当命令帧到来时会引起中断,中断子程即通过altera_avalon_1553B_getframe()解读命令帧的内容,确定是读取还是写入,读取或写入数据的长度,数据的特征作为下次读取的标志,确实无误后,开始读取或写入。

存储器的管理与其他应用中不同的有两点:在每次写入后,必须将写入的数据作一个标志,以方便以后读取;另外,还要计算剩余存储的容量,在下一次需要写入数据时判断是否可以容纳下本次存储。1553B的主结点在使用完毕数据后也需要提供信号来清空存储以释放资源。

作者:杨俊 中国移动通信集团江西有限公司 来源:《今日电子》2008年01期

上一篇:基于Windows

CE的远程数据采集与控制系统开发

下一篇:基于STWD100xP

WTD嵌入式系统抗EMC技术