- 易迪拓培训,专注于微波、射频、天线设计工程师的培养

多频连续波雷达数据实时压缩算法设计

摘要:随着测试参数种类增加,测试环境越来越复杂,海量雷达数据与有限存储容量之间的矛盾日益明显,实时数据采集与压缩技术可以缓解这一矛盾的加剧。雷达数据采集系统采取了基于FPGA的LZW实时无损压缩算法。该算法能够实现追求采集信号精度的同时减低算法难度,已成功应用于某飞行测试实验,性能指标满足应用要求。

多频连续波雷达是一种新体制雷达,能够同时发射多个频率的连续波正弦信号对多个目标的速度、加速度、距离、方位角、俯仰角等多组参数目标进行探测。具有设备简单、体积小、重量轻、功耗低等优点[1]。

对于连续波体制雷达,目标参数多、信号处理的实时性强是其最显著的特点。海量的回波数据使得存储操作变得非常困难,并且也不易进行数据分析。数据的实时采集压缩技术可以解决这一问题。由于雷达信号较为敏感,在大多数情况下雷达信号都需要先记录,再事后取证、分析,所以只能采用实时无损压缩。因此,要求多频连续波雷达数据采集系统信号处理实时性好,处理数据量大,在追求目标采集测量精度的同时降低信号处理算法的复杂度,利于工程实现。

当前有很多压缩与解压缩方法都是基于软件实现的,都是对数据进行后期处理。这种方法执行速度慢,耗费大量的CPU资源。采用硬件实现数据的实时无损压缩能够将高速信号变成缓变信号进行传输,降低通信的信道容量,提高数据的可靠性。在雷达信号数据采集系统中,完成数据的海量存储并提高总线的数据传输速度应采用硬件实现数据的实时无损压缩。

1 数据压缩算法比较

数据压缩算法有不同的分类方法,根据压缩算法是否可逆可以分为可逆压缩与不可逆压缩。其中可逆压缩也叫无失真编码或无损压缩。不可逆压缩叫做失真编码或有损压缩。由于人的感觉器官对于图片、声音或视频中的某些信息的丢失难以察觉,一般采用有损压缩算法可以节约大量的存储空间。主要有预测编码、多分辨率编码、分型图形编码等。无损压缩算法主要有哈夫曼编码、算术编码、游程编码和LZ编码等[2]。其中哈夫曼编码与算术编码均根据源数据发生的概率进行编码,需要对压缩数据进行统计,处理过程缓慢,实时性差;游程编码只有在字符连续出现4次以上才能获得比较好的压缩效果,不适用于压缩雷达回波信号。LZ编码是基于字典的模式,用单个代码代替字符串,数据流式输入,对数据源无分块要求,实时效果好,解压完全可逆。LZ编码包括LZ77、LZ78和LZW(Lempel-Ziv-Welch Encoding)。本文根据雷达回波数据的压缩要求选用LZW无损压缩算法。

2 雷达数据采集系统硬件实现

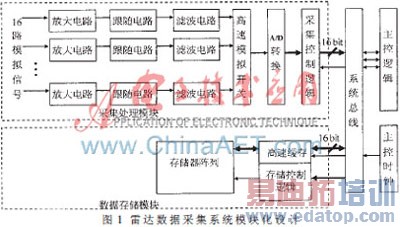

本文介绍的多频连续波雷达数据采集系统中16路模拟信号经过放大、跟随、滤波处理后经高速模拟电子开关进入高速ADC,输出16bit数字量。数字量的缓存与处理由采集处理模块中的采集控制逻辑(FPGA)实现。压缩后的数据在主控模块的控制下经高速系统总线写入数据存储模块中的存储器阵列。原理框图如图1所示。

3 基于FPGA的LZW算法设计

3.1 LZW数据压缩算法

LZW数据压缩算法是一种新颖的压缩方法,具有实时性,压缩效率高,可对不同的数据流进行自适应压缩,对于缓变、重复性高的数据流,随着数据量的增大, 压缩效率能显著提高。LZW算法有三个重要的对象:数据流(CharStream)、编码流(CodeStream)和编译表(String Table)。在编码时,数据流是输入对象,编码流是输出对象。数据流是指被压缩数据,编码流是指压缩后输出的代码流,编译表存储的是数据的索引号,相同块的数据只输出第一块的索引号,从而实现数据的压缩。

LZW压缩算法的基本原理是提取出待压缩数据中的不同字符,基于这些字符创建一个编译表,然后用编译表中的字符索引替代原始数据中的相应字符,从而减少原始数据的大小。其中编译表不是事先创建好的,而是根据原始文件数据动态创建的。

LZW压缩算法的基本思想是建立一个串表,将输入字符串映射成定长的码字输出,通常码长设置为12bit,也可设置为15bit或者18bit。串表具有"前缀性":假设任何一个字符串P和某一个字符S组成一个字符串PS,若PS在串表中,则S为P的扩展,P为S的前缀。字符串表是动态生成的,编码前先将其初始化,使其包含所有的单字符串。在压缩过程中,串表中不断产生压缩信息的新字符串,存储新字符串时也保存新字符串PS的前缀P相对应的码字。在解压缩过程中,解码器可根据编码字恢复出同样的字符串表,解出编码数据流[3-4]。

3.2 FPGA模块化设计

FPGA具有运行速率快,逻辑资源丰富,片内RAM资源丰富,通用性好等特点。用FPGA实现LZW算法需要解决以下几个关键问题[5-6]:(1)字典的生成。通常采用FPGA片内存储单元生成RAM;(2)字典的维护与更新:在压缩过程中,对于一个新的字符串要在对字典进行查找后,根据字典中是否已经存在来决定是否更新字典,这一过程必须利用FPGA片内逻辑单元完成,因而过于复杂的字典需要耗费大量逻辑单元,不宜采用FPGA模块化设计;(3)压缩编码流的处理:由于压缩算法改变了原始数据的编码格式,需要在压缩过程中添加一些标识符,使得在解压缩过程中能够完全还原原始数据。并且在压缩编码输出数据时,需要根据存储器件或传输总线的数据位宽度进行重新编码。

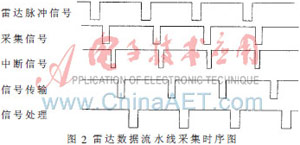

在雷达信号的采集系统中,信号采集与处理的控制时序是保证数据正确传输的关键。大多数雷达数据的信号处理都采用流水线的数据处理方式,如图2所示。

雷达数据通过采集系统的高速A/D采集进入到存储模块时需要向控制器件发出中断信号,再将数据写入到存储器中等待信号处理模块对雷达数据进行分析、压缩处理[7]。这种发出中断信号的流水线采集方式由于受到采集数据周期长的限制,不利于数据的实时压缩,必然导致数据总线实时传输速率的降低,不能满足待采集信号量日益增大的要求。

为节约FPGA的I/O引脚,缩小系统体积,本文所设计的采集系统首先将高速ADC转换后的16bit数字量分高8bit和低8bit写入FPGA内的数据缓存模块,时序控制模块完成将缓存数据依次送入LZW算法模块及各模块之间的时序控制操作,压缩后的数据再经过数据宽度转化模块写入到系统总线。

由于本系统需要大量的片内的Block RAM构成数据缓存模块和字典存储模块,因此采用Xilinx公司的Virtex-E系列的XCV400E,该器件具有丰富的RAM资源,共有40个Block RAM,每个Block RAM存储容量为4096bit。Block RAM可以用作FPGA片上和片外缓冲的FIFO,高速并行访问的缓冲存储器和总线宽度转换器等。设计选用的是双口RAM,每个端口都有独立的控制信号,并且每个端口的数据总线宽度可以独立配置。在本文设计的采集系统中数据缓存模块及数据宽度转换模块选用双口RAM,对于字典存储模块选用单口RAM构成。FPGA片内集成功能模块如图3所示。

由图3可知,FPGA主控逻辑内部主要有以下四个模块。

(1)输入缓存模块:该模块由FPGA片内集成的2个高速FIFO构成,数据采用循环写入方式,最大限度地实现数据的实时处理。

(2)时序控制模块:完成对数据缓存模块的读写操作和为其他模块提供时序控制信号。

(3)压缩算法实现模块:实现字典的初始化,字符串查找、判断、更新,输入数据流的编码,输出代码生成等功能;

(4)字典存储模块:用于存放字典数据信息。

在字典存储模块中选用20片Block RAM并联构成20bit数据宽度、4K深度的字典存储区。每个存储区存放20bit宽度字符,包含两部分:头部为12bit的前缀字符P,尾部为8bit的当前字符S。输出为12bit编码。

(5)数据宽度转换模块:将压缩后的12bit编码数据转换为与系统背板总线对应的16bit数据宽度。

设计中采用把4个双口RAM并行连接构成16bit数据宽度、1K深度的高速FIFO。压缩后的12bit输出码流经过数据宽度转换模块组合成16bit数据写入系统总线。

3.3 LZW算法工作流程

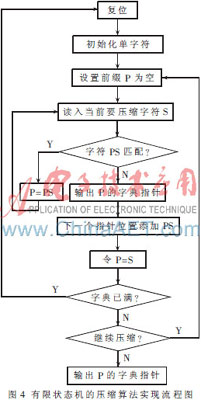

本文所设计的采集系统借鉴了流水线采集方式状态机实现简单的优点,算法采用VHDL语言实现有限状态机,压缩算法流程如图4所示。

状态机首先完成初始化过程,物理地址000H~0FFH分别存放对应的0~255。初始化完成后,状态机进入压缩编码循环,读入当前字符,若该字符与字典中的某个字符匹配,再读入下一字符;若不匹配,把该字符加入到当前字符串中,输出前缀的字典指针到输出码流。反复执行该过程,直到编码结束。

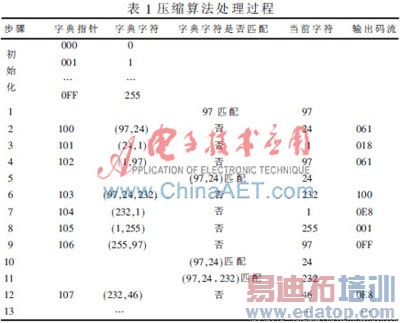

以字符串流97,24,1,97,24,232,1,255,97,24,232,46……为例,表1给出LZW压缩算法的处理过程。输出码流为061,018,061,100,0E8,001,0FF,0E8……,其中字典指针及输出码流均以16进制表示。

3.4 测试结果分析

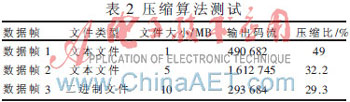

本文设计的多频连续波雷达数据采集系统中的控制逻辑采用Xilinx公司的Virtex-E系列FPGA器件XCV400E,系统时钟频率100MHz,分别选取三种不同类型的雷达数据帧进行压缩算法测试,如表2所示。其中数据帧1为1MB的雷达视频回波文本文件数据,杂波信号较多;数据帧2为5MB的雷达视频回波文本文件数据,杂波信号较少;数据帧3为10MB的二进制雷达数据。

由测试结果可以看出,LZW算法对于杂波信号较少的缓变雷达回波信号的压缩效果最好。对于杂波较多的数据实现无损压缩可进一步对LZW算法进行优化。例如固化初始化过程,可以节约压缩时间和简化控制时序;或是对于出现频率高的字符,记忆其字典指针及出现位置,不必每次都从字典的起始处开始查,简化算法的复杂度。

本文介绍了基于FPGA的LZW算法在雷达回波信号压缩中的应用,利用FPGA内部丰富的Block RAM资源,在片内集成高速数据缓存及字典存储模块实现对海量雷达数据的实时采集、压缩处理。算法通过采用VHDL语言有限状态机实现,可移植性强,并可在线升级。该算法已成功应用于某飞行测试实验中。

参考文献

[1] 戴奉周,冯维婷,沈福民.数字多频连续波雷达信号处理中的关键算法[J].雷达科学与技术,2005,6(3):177-180.

[2] SALOMOND.数据压缩原理与应用[M].吴乐南,等,译.北京:电子工业出版社,2003.

[3] 蓝波,林小竹,籍俊伟.一种改进的LZW算法在图像编码中的应用[J].计算机工程与科学,2006,28(6):55-57.

[4] 郭晓岩,郝永胜. LZW无损压缩算法在计算机取证中的应用研究[J].测控技术,2006,25(11):64-67.

[5] LONMB,LEEJF,JANGE. A lossless data compression anddecompression algorithm and its hardware architecture[J].IEEE Trans,VLSI. 2006,14(9):925-935.

[6] 陈晋敏,黄春明,周军. 激光雷达数据无损压缩的FPGA实现[J].计算机测量与控制,2007,15(1):100-102.

[7] 尹志勇,焦新泉,任勇峰.雷达视频回波信号实时采集、压缩转发装置[J].计算机测量与控制,2010,18(2):479-481.

作者:刘鑫 任勇峰 来源:《电子技术应用》2011年第8期

上一篇:CPLD实现GPIB控制器的设计

下一篇:以太网的远程控制信号调理系统