- 易迪拓培训,专注于微波、射频、天线设计工程师的培养

基于DSP平台的多音平行体制调制端的实现

摘要:以32音并行体制为例,利用DSP平台实现了多音并行体制的调制端,给出了其主要模块的具体实现方法。由于并行体制技术成熟、成本低、高性价比对提高数据传输速率、消除多径衰落有益。

短波通信中常采用多音并行和单音串行两种体制来进行高速数据的传输。单音串行体制仅采用一个载波,串行发送数据信号。由于每个码元占据了整个频谱,码元宽度窄,当传输高速数据时,实现复杂,且码间串扰严重。而多音并行体制的主要思想就是把高速串行信道分裂成许多低速的并行信道,以适应短波信道低速传输的特性,在每个子信道上传送一个副载波,采用频分正交调制,用多个副载波并行传输的方法提高速率。并行体制的传输,是采用加宽码元宽度,使其远大于多径时延,消除多径衰落的影响。并行体制技术成熟、成本低,具有较高的性价比。本文以32音体制为例说明短波并行体制调制端的DSP具体实现方法。

1 32音并行体制调制端的设计

本并行体制在音频频带内采用32个正交副载波音,对比特同步数据传送采用正交差分相移键控(QDPSK)调制。

具体设计要求:

(1)在数据输入端口接收不同速率的串行二进制数据:300 b·s-1,600 b·s-1,1 200 b·s-1;

(2)对接收到的二进制数据完成前向纠错(FEC)编码和交织;

(3)每个单音上采用QDPSK调制;

(4)采用32个正交载波音,每个音相隔56.25Hz;

(5)采用某种分集方式。

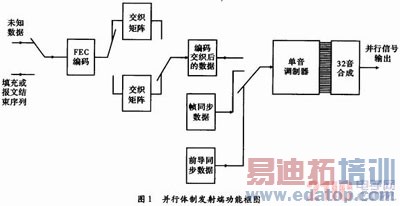

图1为多音并行体制下发射端功能框图。

2 软硬件平台介绍

本文实现多音并行调制端的硬件平台如图2所示,主要由计算机PC、DSP-TMS320C6416、A/D芯片TLV320AIC20组成。DSP通过多通道缓冲串口1(McBSP1)与计算机相互通信,同时通过多通道缓冲串口0(McBSPO)与TLV320AIC20相互通信。

本平台采用的TMS320C64xx系列是2000年3月TI正式发布的定点系列,主频1.1GHz,处理速度接近9 000 MI·s-1总体性能比C62xx提高了10~15倍。

TLV320AIC20是TI公司生产的一款低功耗高性能的双通道A/D芯片,可含有两个16位A/D通道和两个16位D/A通道,完成模拟与数字话音的转换工作,软件可编程寄存器内含有6种可编程的控制寄存器,配置方便。

软件平台采用CCS(Code Composer Studio)系统,其包含一整套用于开发和调试嵌入式应用的工具。它包含适用于每个TI器件系列的编译器、源码编辑器、项目构建环境、调试器、描述器、仿真器以及多种其它功能。

3 并行体制关键模块的具体实现

3.1 核心模块-FFT

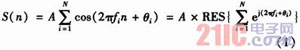

由于发送信号是一组余弦函数的叠加。假设信号是由一组N个频率为f1,f2,f3,…,fN,初始相位为θ1,θ2,θ3,…,θN,幅度为A的余弦信号,故其叠加后的信号为

其中,RES[]是取函数的实部。

从式(1)中可以看出,利用反傅里叶变换(IFFFT)可以方便地产生前导序列和生成调制信号方便。同时反傅里叶变换在DSP中运算量不大,并可以直接调用傅里叶变换,将输入信号的格式稍加处理即可得到反傅里叶变换的结果。

本文设计的并行体制要求32个数据音中,相邻两个音之间相隔56.25 Hz并且正交,这32个数据音分别为450Hz,506.25Hz,…,2193.75Hz。同时采用128点的快速傅里叶变换实现前导序列和数据信息的调制。由于32个数据音中最大频率是2193.75Hz,根据Nyquist采样定理,采样速率fs应大于信号最大频率的2倍,本文使用fs=7200Hz的采样速率。

由于设计的调制后码元周期是22.5ms,在7200Hz采样率的条件下,需要162个样点构成一个码元,而IFFT的点数是128<162,所以对于IFFT的输出需要补充34点才能构成162点满足一个码元要求。补充样点的方法是:直接从IFFT输出数据的最前面截取34点补充到128点以后,这样做的同时也能保证一个码元内信号相位的连续性。

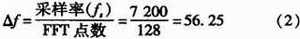

由于采用128点的IFFT和7200的采样率,故IFFT中每个频点之间的频率间隔为

可以看出56.25Hz的频率分辨度正好是32个数据音之间的频率间隔,且32个数据音都是56.25Hz的整数倍,这样便于实现数据音的调制。

在DSP中利用FFT模块,将输入的复信息实部虚部的顺序改为先虚部再实部。根据32个音的频率f与频率分辨度△f的比值得到频点位置n= fi/△f,然后在对应的频点处填写复信息 。这样就能通过IFFT得到需要的调制信息。各数据音对应的频点位置和编号,如图3所示。

。这样就能通过IFFT得到需要的调制信息。各数据音对应的频点位置和编号,如图3所示。

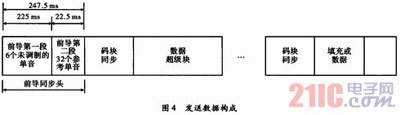

3.2 前导同步数据构成

在数据传送之前应发送同步先导信号,同步先导信号包含两段。第一段持续10个码元(码元宽度225ms),并包括675Hz、900Hz、1125Hz、1518.75Hz、1743.75Hz和1968.75Hz共6个等幅未经调制的数据音,幅度为3。第二段应持续一个信号码元,包括32个数据音且幅度为1。最后一段前导序列产生了后续信号需用的启动相位基准。

发送端一次发送的数据构成,如图4所示。前导序列的发送包含了11个码元,在进行前导序列的发送时,要保证每一部分都满足规定的码元持续时间。如果前导序列的构成不准确或持续码元不足,都直接影响到接收端对信号的捕获。

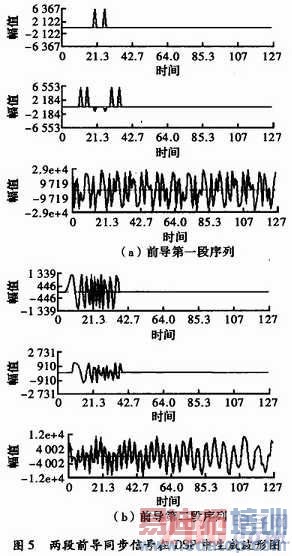

图5所示为两段前导同步信号在DSP中的生成图。在每段前导序列生成图中前两个是IFFT时在各个频点填充的复数值,第3个是经过IFFT后前导序列波形图。

3.3 数据调制信号的实现

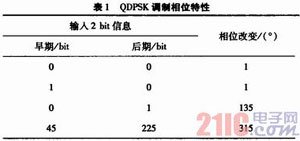

数据段发送32个已调制的数据音信号。各信号音的初始码元相位已经确定,而后用数据比特流对32个数据音进行调制。各数据音采用的调制方式是QDPSK调制。QDPSK是正交差分相移键控调制,是一种相对移相的调制方式,它利用前一个码元相位为参考,根据已知序列比特流进行调相,如表1所示。

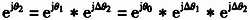

假设某个数据音调制的初始相位为θ0,理论上,首先根据第一个码字查表1得到其△01,计算IFFT要填充的复数为,而后进行第一个码元的IFFT。再根据第2个码字查表得△θ2,计算IFFT要填充的复数为 ,而后进行第2个码元的IFFT。以此类推,完成所有码元的调制。在实际实现时,在DSP计算

,而后进行第2个码元的IFFT。以此类推,完成所有码元的调制。在实际实现时,在DSP计算

时,会出现随着码元数的增加,cos()*cos()的值越来越小,最后计算出的

时,会出现随着码元数的增加,cos()*cos()的值越来越小,最后计算出的 误差较大。为避免这种情况,应减少复数相乘的次数。

误差较大。为避免这种情况,应减少复数相乘的次数。

具体的做法是:

(1)根据QDPSK的星座图对待调制的码字进行编码:00→3,01→1,10→5,11→7。

(2)将前后码字所对应编码后的码进行模8加,即得到当前码字所对应的相位信息码。相位信息码只有8种可能{0,1,2,…,7},对应的△θ分别是{0,π/4,π/2,…,7π/4},这样查表即可得到△θ。

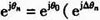

(3)计算 ,这样只需计算一次复数乘就可以得到做IFFT所需的信息。

,这样只需计算一次复数乘就可以得到做IFFT所需的信息。

(4)记录本码字所对应的相位信息码,以用于下一个码字的相位信息码的计算。

3.4 前向纠错(FEC)编码

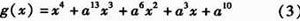

所有未知输入数据应具有附加的冗余位,用以纠正由传输媒介引起的错误。校验位由一个缩短的Reed—Solmon码(15,11)来计算,其生成多项式为

其中,a是伽罗瓦域的一个非零元素,GF(24)为GF(2)模形成的多项式域。所采用的是缩短为(7,3)的RS编码。

RS(7,3)编码采用3位16进制码生成4位16进制的校验监督位,即12bit信息编码生成16bit校验监督位,也就是RS(28,12,16)编码。为了减小DSP的开销,采用的编码思想是预先建立校验表而后逐位判决逐位编码的方式。具体步骤如下:

(1)建立校验表。编写信息位是0800H,0400H,0200H,…,0008H,0004H,0002H,0001H所对应的校验位分别是:03959H,08DBDH,04FCFH,02E6EH,…,0156FH,0983EH,0DC87H。这样可以建立校验表:

.int 03959H,08DBDH,04FCFH,02E6EH

.int 037EEH,08A77H,045AAH,02855H

.int 02ACDH,0156FH,0983EH,0DC87H

(2)根据校验表逐位编码。假设需要编码的信息是A81H共3位16进制信息,将其转换二进制数为101010000001B。第1位是1,则取A1=02C7AH,第2位是0,则取A2=0,第3位是1,则取A3=0935BH,第4位是0,则取A4=0,…以此类推得到A1,A2,…,A12,将这12个校验码进行异或得到这3位信息的4位校验码。

3.5 交织

交织是一种差错控制技术。它的目的是使误码离散化,将突发差错信道变为离散差错信道,再通过纠正随机差错来改善数据传输质量。原理把信息码流在时间顺序上按一定规则打乱,即相互穿插交织后再发送到信道中去。若交织后的码流出现突发差错,再经过解交织还原成原来的码流顺序,则将突发连片差错分散成随机差错,更加容易进行纠错。由于接收机在收到了整个交织块并进行解交织后才能解码,所以交织带来一个固有延时。

选取每种速率3种交织度来实现。分别是无交织(交织度为1)、短交织(交织度为4)、长交织(交织度为36)。

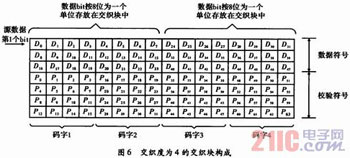

这里所说的交织度(1、4、36)指的是交织块中一行所包含的4 bit码字数。以短交织为例,说明一个交织块的构成。

源数据以8bit作为1个单元,按列向交织区填充,如图6所示。RS编码时取4bit×3行数据作为1个码字进行编码,形成4 bit×4行的校验位。图6中对信息位(D0,D1,D2,D3,D8,D9,D10,D11,D16,D17,D18,D19)进行RS(7,3)编码后生成校验位为(P0,P1,P2,P3,P4,P5,P6,P7,P8,P9,P10,P11,P12,P13,P14,P15),并且依照图中的格式存放在交织块的对应位置。当一个交织块填充满后,就可以按行进行一个交织块数据bit的输出,(D0,D1,D2,D3,D4,D5,…,P47,P60,P61,P62,P63)。

3.6 分集方式

分集技术是通过多个信道接收到承载相同信息的多个副本,由于多个信道的传输特性不同,信号多个副本的衰落就不会相同。接收机使用多个副本包含的信息能比较正确的恢复出原发送信号。本系统采用的是包含时间和频率分集的方法。

在不同的数据速率下,1个码元所用到的数据字大小不同,可以将300~1200 bit·s-1各种速率情况总结如下:1200bit·s-1速率时不做分集,一个数据字需要64bit信息;600bit·s-1速率时,一个数据字需要32bit信息;300bit·s-1对应的是16bit的数据字。换句话说,就是在300bit·s-1数据速率下,只要有16bit新信息,就可以进行一个码元的调制。数据速率为600bit·s-1的情况,如表2所示。

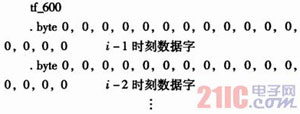

在600bit·s-1数据速率情况下,要求在1~8及17~24号数据音传送当前数据字,9~16及25~32号数据音传送的是之前第8个码元传送的数据字。在DSP内存中开辟一个空间存储过去8个码元用到的数据字。

每次只要从i-8时刻提取数据字填充到9~16及25~32号数据音,而后进行32音调制即可实现带内时间频率分集。

4 结束语

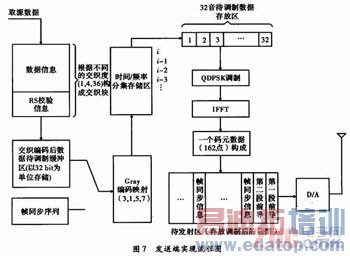

发送端在DSP中实现的具体流程,如图7所示。

具体实现时遇到的问题和难点:

(1)交织度、RS编码方式、带内时间/频率分集方式都随数据的不同而不同,所以要考虑到相对应程序的通用性,设定入口参数和参数下载的过程,这样减小程序代码段的开销,但是增加了编程的复杂度。

(2)从源数据区向交织区填充数据时,要注意剩余bit的保存。从交织区向待调制区填数据时,要注意剩余bit的保存。

(3)在超级块和超级块的衔接处,存在剩余bit调制发送的问题。要把当前超级块所剩下的bit全部调制发送完,才能进行下一个超级块的构成和发送。

作者:何纬 中国电子科技集团 来源:电子科技