- 易迪拓培训,专注于微波、射频、天线设计工程师的培养

基于FPGA的智能仪器远程控制系统设计

摘要:为实现智能仪器的远程控制,提高控制系统的速度,采用现场可编程门阵列(FPGA)芯片、USB芯片等实现了智能仪器远程控制系统的设计。重点介绍RS232与USB的接口转换原理及FPGA程序设计和仿真。系统采用先入先出存储器和有限状态机实现了RS232与USB的接口转换,并实现上位机的控制、数据处理等功能。系统可大大减少上位机的工作量,不仅可以用于实验室也可应用在工业生产中。

目前智能仪器已广泛应用于科研和工业生产当中,但是许多仪器分散在不同的地理位置上,不易操作和维护,并且实时跟踪性能差,人为误差大,数据无法保存,另外大量高档仪表价格相当昂贵。为解决上述难题,在计算机的提示下完成操作,可以减少人为因素造成的损坏,并提高测试数据的准确度。由于智能仪器是RS232接口,上位机用的是USB接口,所以还需由FPGA实现RS232与USB之间的接口转换。由于FPGA可以并行处理,集成度高,可用资源丰富,所以利用FPGA进行数据处理,可以减少上位机的工作量,减少数据处理的时间,还可以缩短设计周期,减小板卡体积,以便于集成到其他板卡上。

1 控制系统及接口简介

1.1 系统功能

在整个系统中,上位机可以实时对系统进行监控,并下发相应的命令。智能仪器传出的数据通过RS232接口传送到FPGA,FPGA根据上位机下发的命令对这些数据进行判决、处理,然后经过USB接口上传给上位机,再由上位机对FPGA处理过的数据进行显示、存储等操作。

1.2 USB接口芯片简介

本设计采用的是CYPRESS半导体公司的EZUSBFX2系列芯片CY7C68013。CY7C68013是一款高性能USB 2.0微控制器,它提供了全面的USB 2.0外围设备解决方案。工作模式有Port,Slave FIFO和GPIFMaster三种,本方案采用Slave FIFO模式。在该模式下,外部控制器(如FPGA)可像对普通FIFO一样对FX2中端点为2,4,6,8的数据缓冲区进行读/写。FX2内嵌的8051固件的功能只是配置Slave FIFO相关的寄存器,以及控制FX2何时工作在Slave FIFO模式下。一旦8051固件将相关的寄存器配置完毕,且使自身工作在Slave FIFO模式下后,外部逻辑(如FPGA)即可按照Slave FIFO的传输时序,高速地与主机进行通信,而在通信过程中不需要8051固件的参与。

1.3 RS232接口简介

RS232C标准(协议)的全称是EIARS232C标准。EIARS232C是用正负电压来表示逻辑状态的,与TTL以高低电平表示逻辑状态的规定不同。因此,为了能够与计算机接口或终端的TTL器件连接,必须使EIARS232C与TTL电路之间进行电平和逻辑关系的变换。实现这种变换的方法可用分立元件,也可用集成电路芯片。该设计用的是MAX3232芯片。

RS232的数据传输格式如图1所示。

图1 RS232标准的数据传输格式

RS232传输格式包含起始位(1b)、有效数据位(8b)、奇偶校验位(0~2b)、停止位(1b)。传输线在空闲时为高电平,因此起始位为低电平,停止位为高电平。

奇偶校验位可设置为奇校验、偶校验或不校验,有效数据位是从低位开始传送。

2 FPGA设计

2.1 USB接口时序

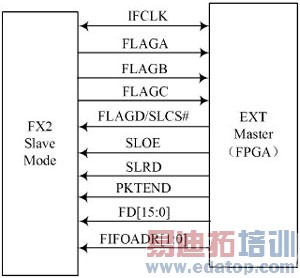

在Slav e FIFO方式下,外部逻辑与FX2的连接信号如图2所示。

图2 FX2 Slave模式下接口管脚连接图

在Slav e FIFO模式下,CY7C68013芯片为端口2,4,6,8 提供满空标志位FLAGA,FLAGB,FLAGC,FLAGD。IFCLK为FX2输出的时钟,可作通信的同步时钟;SLCS为FIFO的片选信号;SLOE为FIFO输出使能;SLRD为FIFO读信号;SLWR为FIFO写信号。对FPGA来说,4个端口分别为4个FIFO。

FPGA检测4个满空标志位来分别对相应的FIFO进行读/写。FPGA可以选择同步或异步读/写,在该设计中采用异步读/写。在异步Slave FIFO写时,时钟由FPGA提供。数据在SLWR的每个有效-无效的跳变沿时被写入,FIFO写指针递增。异步Slave FIFO读时,FIFO读指针在SLRD的每个有效-无效的跳变沿时递增以改变数据。

2.2 FPGA程序设计

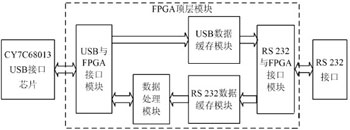

FPGA设计是整个系统的核心部分,由VHDL语言实现。FPGA实现了USB与RS232接口的转换、数据的处理、命令的传输等功能。有了上面的接口时序,便可以进行FPGA设计。FPGA部分的总体设计如图3所示。模块介绍:

USB与FPGA接口模块:USB与FPGA之间的接口转换模块,主要功能为将USB接口传过来的信息缓存到FPGA内部FIFO,并将由数据处理模块处理过的数据传给USB芯片。即产生控制信号读/写USB芯片内部FIFO。可以由读/写FIFO两个有限状态机实现。

以读取CY7C68013芯片内数据为例,根据异步读USB内的FIFO时序图可分为4个状态:空闲态、选择地址态、准备读数据态、读数据态、读取后状态[6] 。在空闲态,当读事件发生时进入选择地址态;在选择地址态,使FIFOADR[1: 0] 指向OUT FIFO,进入准备读数据态;在准备读数据态,如FIFO空,在本状态等待,否则进入读数据态;在读数据态,使SLOE,SLRD有效,从数据线上读数,再使SLRD无效,以递增FIFO读指针,再使SLOE无效,进入读取后状态;在读取后状态,如需传输更多的数,进入准备读数据态,否则进入空闲态。

图3 FPGA总体设计框图

USB数据缓存模块:用来缓存计算机发给智能仪器的指令等信息。是由FPGA芯片的IP核生成的先入先出存储器FIFO。容量为8b*512depth。占用1个块RAM资源。

RS232数据缓存模块:用来缓存由智能仪器发出的数据。是由FPGA IP核生成的先入先出存储器FIFO。容量为8b*512depth,占用1个块RAM资源。

RS232与FPGA接口模块:RS232与FPGA之间的接口转换模块。主要功能为进行串/并和并/串转换。

将USB数据缓存模块中缓存的内容以合适的速率通过串口发给智能仪器,并将智能仪器发出的数据缓存到RS232数据缓存模块中。此模块也是由两个状态机实现。串口通信必须要设定波特率,这里采用的波特率为9600Kb/s,采用的时钟为50MHz,相当于传送1位数据需要约5028个时钟周期,这里采用减法计数器来控制,即计数器计到5028个时钟周期后,就开始传输下一位数据。

数据处理模块:主要功能为根据上位机的指令对RS232数据缓存中的数据做出相应的处理。处理后再向上位机传。主要的处理方式有定时取数、平滑处理等。实现方式由状态机等实现。FPGA顶层模块:主要负责各模块间数据流的流向。以及与外部芯片相连的输入输出信号的定义。

系统在工作时,在采集数据上传上位机时,数据通道为:智能仪器发送的数据通过RS232接口模块存在RS232数据缓存模块中缓存。当缓存到一定的数据量后,再通过数据处理模块连续的读取FIFO中的数据并根据上位机发送的命令进行相应的数据处理,然后将处理的数据通过USB与FPGA接口模块传给USB接口。在上位机下发控制命令时,数据通道为:上位机发送的命令通过USB口传给FPGA的RS232与FPGA接口模块,此模块判断是数据处理指令还是控制仪器指令。如果是数据处理指令,则传向数据处理模块让其按要求进行数据处理。如果是控制仪器指令,则将其存入USB数据缓存模块中,再由RS232与FPGA接口模块读取,转成RS2322格式后传出。由于RS232接口速度比USB接口慢,用FPGA内部的异步时钟FIFO解决速率匹配问题。

将通过RS232传过来的数据缓存在FIFO中,然后存到一定数据量后再全部连续的取出,如此往复,从而实现数据的连续采集及上位机的实时显示。将通过USB传过来的数据放在另一个FIFO中缓存,让FPGA按照RS232的速率进行读取。这样可以防止RS232的速度跟不上USB的速度而产生的数据丢失。

3 仿真结果

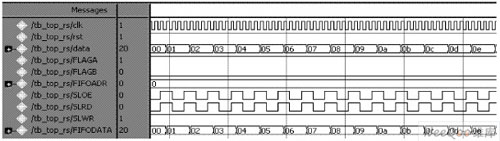

FPGA采用的系统时钟频率为50MHz,仿真工具为Modelsim SE 6.5a,仿真用数据为连续的8b数据。

仿真结果如图4所示。

图4 FPGA读USB内部FIFO仿真图

图4为FPGA读USB内部FIFO的仿真结果,DATA为模拟从USB口接到的数据,该数据已存在于USB芯片的FIFO中。FIFO DATA为FPGA接到的数据,由上可以看出,FPGA可以将USB接受到的数据解析出来。

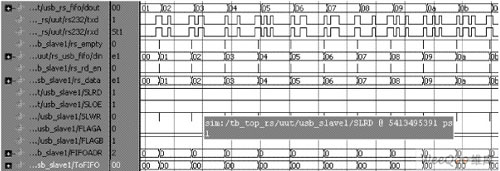

图5为RS232与FPGA接口部分仿真结果。可以看出,由RS232接收串行数据RXD已经转换为并行数据din。程序中是在一个有效字节结束后将其存入FIFO中,由图可以验证。图6顶层模块仿真图,为了验证由FPGA发出的数据能正确的接受到,先由FPGA内部发数据,然后通过RS232的TXD端口发出,让RXD与TXD相连再接收,可以看出发出的数据可以被正确的接收回来并传向USB接口,说明时序正确。

同理可以验证USB端的收发时序。

图5 RS232接收端仿真图

图6 顶层模块仿真图

4 结 语

本文采用FPGA实现了USB与RS232间的接口转换及数据处理的功能。设计中先入先出存储器的运用解决了数据的缓存的和速率匹配问题,有限状态机的运用使得程序设计更加清晰可靠。该设计将复杂的信号运算集中在FPGA中完成,利用FPGA独特的并行处理能力,减小上位机工作量的同时,提高了系统运行速度。

作者:谢燕平 郭静 延凤平 北京交通大学光波技术研究所 来源:《现代电子技术》2011年第4期