- 易迪拓培训,专注于微波、射频、天线设计工程师的培养

基于SOPC的分布式干扰系统嵌入式网关设计

摘要:分布式干扰是对抗现代雷达网、通信网、武器制导网和预警机的有效手段,网络是分布式干扰系统发挥作战性能的重要保证。为了解决分布式干扰系统网络通信的需求,设计了基于FPGA且具有网络通信功能的SoPC,开发了网络应用程序。实验结果证明,该SoPC可实现控制参数和侦察信号时域、频域数据的高速传输,且具有体积小,灵活,成本低,功耗小的特点,可满足分布式干扰系统的设计要求。

0 引言

分布式干扰系统是一种综合化、一体化、小型化、网络化和智能化系统,是将众多体积小,重量轻,廉价的小功率侦察干扰机装置在易于投放的小型平台上,撒布在接近被干扰目标空域地,通过指令启动,自主组网,并根据控制对敌方雷达网、通信网、制导网和预警机等电子信息系统实施接近式侦察和干扰,这将在未来的电子对抗中发挥重要作用。分布式干扰系统采用逼近的分布式网络化结构,形成一种"面对面"的电子战系统,共同完成对敌信号的探测、定位、干扰任务。因此,嵌入式网关是分布式干扰系统研究的关键技术之一。目前国内对分布式干扰系统的研究还停留在理论基础上,而对其关键技术的研究不多。本文首次在现场可编程门阵列(Field Programmable GateArray,FPGA)上设计了应用于分布式干扰系统网关的可编程片上系统(System on a Programmable Chip,SoPC),开发了简化的网络应用程序,研究了分布式干扰系统中的嵌入式网关技术。实验结果表明,本文设计的SoPC在满足分布式干扰系统要求的同时,实现了控制参数和侦察信号时域、频域数据的高速传输。

1 分布式干扰系统对嵌入式网关设计的要求

根据分布式干扰系统的作战运用背景,在设计嵌入式网关硬件平台时应从以下几个方面考虑:

(1)微型化。嵌入式网关应该在体积上足够小,保证分布式干扰系统的小型化。

(2)扩展性和灵活性。分布式干扰系统需要定义统一、完整的外部接口,方便软硬件系统的升级,其嵌入式网关也应具有扩展性和灵活性,可以根据作战环境的需要进行升级。

(3)稳定性和安全性。稳定性要求嵌入式网关能够在给定的外部环境变化范围内正常工作。安全性设计包括代码安全和通信安全,是军事领域应用的基本要求。

(4)低成本。分布式干扰系统的作战应用表明,系统是大量部署且不能回收的,因此就要严格限制包括嵌入式网关在内的重要部件的成本。

(5)低功耗。嵌入式网关的硬件设计直接决定了其能耗水平,还决定了各种软件通过优化可能达到的最低能耗水平。因此,要合理地设计硬件系统,有效降低系统能耗。

(6)具有一定的信号预处理能力。嵌入式系统中微处理器的处理能力较弱,且内存较小,嵌入式网络的速度普遍不高。这就要求嵌入式网关具有一定的信号预处理能力,包括下变频功能和FFT变换功能,以此来提高网络传输的效率。

2 分布式干扰系统中嵌入式网关的硬件设计

嵌入式网关实际上就是一个可实现网络通信功能的嵌入式系统。随着FPGA技术的迅速发展,SoPC作为一种特殊的嵌入式系统,具备软硬件在系统可编程、可裁减、可扩充、可升级的功能,已逐渐成为一个新兴的技术方向。因此,本文在设计分布式干扰系统的嵌入式网关时选用基于FPGA的SoPC解决方案,选用的实验平台为Xilinx公司的ML402开发平台。

2.1 分布式干扰系统中嵌入式网关的硬件组成

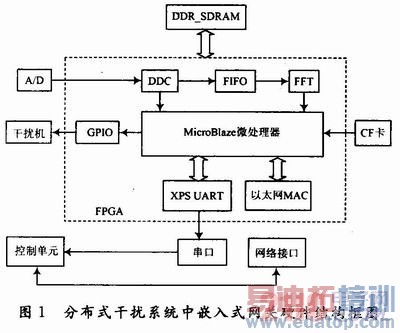

图1表示的是分布式干扰系统中嵌入式网关的硬件组成,这些硬件除A/D、干扰机和控制中心外都集成在一块ML402评估板上。系统以带有32位MicroBlaze微处理器软核的FPGA作为控制中心,处理经A/D变换后的侦察信号数据,然后通过以太网将数据传送到控制中心,并从控制中心传回控制参数。DDR_SDRAM作为片外存储器,用来弥补微处理器内部存储器容量小的缺点;CF卡存储系统软硬件的bit文件和网络配置文件;串口用来控制具有远程控制功能的侦察接收机,也可在调试时输出系统的运行信息。本文设计的嵌入式网关的各功能部件在FPGA内部都以IP核的形式构建并连接,较好地满足了分布式干扰系统对嵌入式网关硬件设计的要求。

2.2 SoPC的片上总线设计

受分布式干扰系统体积和电源能量的限制,其网络通信必须采用猝发通信的方式,这就对嵌入式网关微处理器的处理能力提出了更高的要求。MicroBlaze微处理器的总线是其优于其他同类CPU的重要部分,每种总线都有鲜明的特点和明确的外设。只有合理使用不同的总线来访问不同的外设,且正确地协调这些总线的工作,才能最大限度地发挥MicroBlaze的优势。因此,SoPC的片上总线设计是该系统设计的重点。

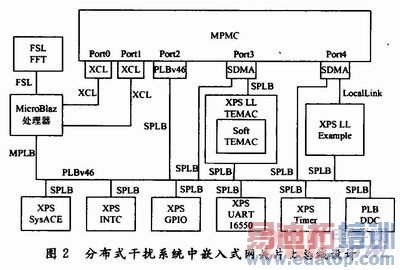

Xilinx以IBM CoreConnect总线通信链为嵌入式处理器的设计基础,提供了丰富的接口资源,主要有处理器本地总线(Processor Local Bus,PLB)接口、高速的本地存储器总线(LMB,Local Memory Bus)接口、快速单连接(Fast Simplex Link,FSL)主从设备接口、缓存链路(Xilinx Cache Link,Xilinx,XCL)接口。PLB总线可将外设IP核连接到Microblaze系统中,常用在速度要求不高的场合;LMB专门用于实现对片上的块RAM的高速访问;XCL则用于实现对片外存储器的高速访问。FSL是Microblaze处理器特有的一个基于FIFO的单向链路,可实现用户自定义IP核与MicroBlaze内部通用寄存器的直接相连,一般用在传输速度要求较高的场合。

在本文设计的分布式干扰系统的嵌入式网关中,SysACE CF卡、中断控制INTC、GPIO和串口UART与MieroBlaze处理器之间只进行参数传递,对速度要求不高,因此使用PLB总线与MieroBlaze处理器和多端口内存控制器(Multi Port Memory Controller,MPMC)相连;MPMC与Mic-roBlaze处理器之间使用XCL相连。自定义IP核FFT输出信号的频谱数据,对传输速度要求很高,因此使用FSL总线与MicroBlaze内部通用寄存器直接相连。DDC输出信号的时域数据,对传输速度要求最高;为满足传输速度要求,本文参照以太网控制器Soft TEMAC开发了XPS_LL_Exam-ple IP核,通过该IP核的LocalLink接口将信号的时域数据传输到MPMC中进行处理。分布式干扰系统的嵌入式网关片上总线设计如图2所示。

作者:薛慧敏 武传华 路后兵 来源:现代电子技术

上一篇:3G移动语音编码标准

下一篇:WLAN芯片的指数回归技术