- 易迪拓培训,专注于微波、射频、天线设计工程师的培养

可变速率Chirp-UWB信号产生系统的设计和实现

(3)倍频器选用Mini公司的AMK-3-452+[8],该芯片输入频率范围为1.0 GHz~1.5 GHz,输出频率范围为3.0 GHz~4.5 GHz,对二次、四次谐波抑制高达55 dB,对三倍频输出信号衰减15 dB。三倍频后,输出中心频率为3.6 GHz,带宽为600 MHz的Chirp-UWB信号。

(4)由于倍频器没有对输入信号进行滤波,在倍频器的输出后面增加了Mini公司HFCN-3100+型号的高通滤波器,它对带外信号的抑制达到30 dB。从图8中可以看出,信号带外抑制接近30 dB,可以满足系统正常通信要求。

4 系统性能和非理想因素分析

4.1 系统性能分析

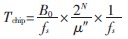

该系统工作时钟为400 MHz,最大频率分辨率为:400 MHz×(1/216)=6.104 kHz,产生基带chirp信号的带宽范围为4 MHz~100 MHz。当Chirp基带信号的扫频带宽为B0时,其时宽可以表述为:

其中fs为采样频率,N为相位位宽,μ″为频率增量。对于产生基带带宽为100 MHz的chirp信号,当频率增量μ″=1时得到扫频信号的最大时宽,Tchip=40.96 μs;当频率增量μ″=128时得到最小时宽,Tchip=0.32 μs。因为当μ″>128时,基带采样点之间的频率间隔将大于128×6.104 kHz=781.25 kHz,经过上变频和倍频后,频率间隔将进一步增大,反映到输出信号上的特征是信号频谱不连续,脉冲压缩增益和频谱压缩增益急剧下降。所以该系统产生带宽为600 MHz(基带100 MHz)的chirp-UWB信号的最低码片速率为24.414 Kchip/s,最高码片速率可以达到3.125 Mchip/s,码片速率的步进为24.414 Kchip/s。

4.2 系统的非理想因素分析

系统的每个组成部分都可能存在非理想因素。本文主要针对CORDIC算法、DAC、正交调制器和倍频器存在的非理想因素做一定的分析。

CORDIC算法的非理想因素主要由流水线结构中的移位器和累加器位数有限和流水结构级数有限造成。前者导致舍位误差,后者造成旋转角度误差。对于chirp信号,因为频率随着时间改变,每次累加的相位值不同,不易产生周期性误差信号,所以在频域上不会形成杂散频率分量,但会抬高系统的整体噪声。在本方案中,CORDIC迭代运算流水结构为13级,移位器和累加器位宽为16。经过13次迭代后收敛,角度误差小于0.005 493°,幅度误差小于10-6。

DAC的非理想性是指DAC的积分非线性、差分非线性、DAC转换过程中出现的毛刺、时钟泄漏和上升时间、下降时间等[9,10]。低速数模转换时,DAC的非理想性对输出信号的影响主要来自幅度的有限位量化,影响不显著;但随着时钟的提高,DAC的非线性会逐渐成为影响频谱质量的主要因素,特别是当DAC的上升时间和下降时间与时钟频率可以比拟时,DAC的动态特性会给输出信号频谱带来杂散分量。本方案中,双通道16 bit DAC采样率在380 MS/s~460 MS/s范围时,输出信号相对稳定,具有73 dBc的增益。为了最大限度地减弱非理想因素对DAC运行的影响,本方案做了如下工作:

(1)DAC与FPGA共用一个400 MHz的时钟源来保证其运行的同步。

(2)要求DAC两路输入输出的布线长度一致以减少两路输入输出信号幅相的差异。

(3)对DAC设置2倍插值以提高过采样增益。

(4)利用DAC自带的增益控制和失调校准功能来提高两路输出信号幅相的一致性。

正交调制器的非理想因素主要是由输入I、Q两路正交基带信号的直流偏置差异和幅相不平衡引起载频泄漏和镜像分量[11]。载频泄漏对于信号频谱的影响表现在频谱中央出现单根谱线,镜像干扰则表现为带内出现粗糙起伏。在本方案中,对镜像和载漏分量的抑制大于-41 dB,镜像和载漏经匹配滤波后趋于发散,主要形成噪声基底,所以对信号的脉冲压缩和频谱压缩性能影响很小。但当正交调制器对镜像和载漏的抑制小于-35 dB时,经过倍频后镜像和载漏的影响将得到放大,对输出信号频谱质量影响严重。另外,经M次倍频后,信噪比和杂噪比都将损失20lgM dB[12]。

本文利用CORDIC迭代运算结合正交上变频和倍频技术,实现了带宽和时宽可控的可变速率Chirp-UWB信号产生系统。相对于采用查找表法实现相同带宽、相同精度的基带线性调频信号,CORDIC算法多消耗了0.5%的逻辑单元,但节省了13%的存储器资源,并且所产生的信号同样能达到查找表法产生信号的性能,且参数设置更为灵活。经测试,该方案产生的信号波形稳定,输出信号的脉冲压缩和频谱压缩性能良好,已成功应用于某超宽带通信系统。

参考文献

[1] 徐春香,刘军.基于FPGA的线性调频信号产生器设计[J].电子测试,2009(10):49-52.

[2] 熊跃军,黎向阳,罗鹏飞,等.宽带脉冲压缩信号产生系统的设计与实现[J].现代雷达,2006,28(1):68-70.

[3] VOLDER J E.The CORDIC trigonometric computing technique[J].IRE Trans.Electronics Computers.1959,8(3):330-334.

[4] ANDRAKA R.A survey of CORDIC algorithms for FPGA based computers[C].Proceedings of ACM International Symposium on FPGA.Mentery,USA,IEEE,1998:191-200.

[5] Stratix III device handbook[EB/OL].http://www.altera.com,2009(2).

[6] Analog Devices Inc.AD9779 data sheet[EB/OL].http://www.analog.com/zh/index.html,2007.

[7] Analog Devices Inc.ADL5372 data sheet[EB/OL].http://www.analog.com/zh/index.html,2006.

[8] X3 Frequency Multiplier[EB/OL].http://www.minicircuits.com,2008.

[9] 费元春,苏广川,米红,等.宽带雷达信号产生技术[M].北京:国防工业出版社,2002.

[10] ESSENWANGER K A.Slewer fractional-order-hold:the ideal DAC response for direct digital synthesizers[A]. Proceedings of the 1998 IEEE International Frequency Control Symposium[C].1998:379-389.

[11] 胡仕兵,汪学刚,姒强,等.超宽带LFM信号数字产生系统的误差分析[J].电子科技大学学报,2008.

[12] 李衍忠.超宽带脉压雷达信号产生系统研究[D].成都:电子科技大学,2000.

来源:电子技术应用