- 易迪拓培训,专注于微波、射频、天线设计工程师的培养

遥测舱信号源的设计与实现

YLVDSD:发送16位数据,传送系统给图像采集设备的所有数据,每个数据位宽度与时钟的半个周期等宽;

YLVDSS:发送同步信号,每字同步,与首数据最高位同时发出,宽度为半个时钟;

YLVDSC:时钟信号,始终保持。

所有的数据以行时间为基准,即每62.5μs发送一组128个数据(以同步信号为基准计数)。共发送130行,其中正程128行发送图像数据,逆程两行发送信息字。

采用VHDL语言编写程序,使FPGA输出固定时序的LVTTL电平的3路信号,经过一片LVDS接口芯片后,转为LVDS信号。

LVDS接口芯片采用National Semiconductor公司的DS90C031,它是四路LVDS线驱动器,单电源5 V供电。

3.2 并行数据

并行数据是以信息帧的形式沿字节多路转换通道发送。信息更新周期为10 ms,每个更新周期传送128个信息字。这些信息字分成2个子帧,每帧64个字,每5 ms发送一子帧。信息字为24位,包括8位地址、16位数据,这样,并行数据的数字遥测信息速率为307.2 Kb/s。

并行数据的数字遥测信息字的结构如图3所示。

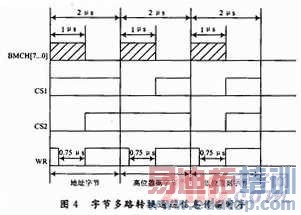

并行数据采用8位并行传输,每个信息字的三个字节分三次沿8位总线分时发送。伴随信号CS1,CS2的不同组合构成地址字节、高位数据字节和低位数据字节的区分标志,信号WR表明信息的发送。地址按00~7F循环发送,数据按0000~9FFF循环发送,8位总线信号、伴随信号和写信号传输均由245作驱动,由这些信号的信号线电压的变化形式表示的信息传输时序如图4所示。

从图4可以看出,一个信息字节的传输时间是2μs,一个信息字的传输时间是6μs。相邻两个信息字之间的间隔时间是10μs。

并行数据信息在5 ms周期内完成后发送,每个周期发送信息的时间大约为640μs。

采用VHDL语言编写程序,使FPGA输出固定时序的LVTTL电平的3路信号,经过2片总线驱动器后,转为TTL电平的并行数据信号。

作者:中国空空导弹研究院 吴静 来源:电子设计工程

上一篇:甄别IPv4和IPv6报头的不同

下一篇:LTE语音解决方案三足鼎立