- 易迪拓培训,专注于微波、射频、天线设计工程师的培养

基于FPGA技术的存储器设计及其应用

复杂可编程逻辑器件—FPGA技术在近几年的电子设计中应用越来越广泛。FPGA具有的硬件逻辑可编程性、大容量、高速、内嵌存储阵列等特点使其特别适合于高速数据采集、复杂控制逻辑、精确时序逻辑等场合的应用。而应用FPGA中的存储功能目前还是一个较新的技术。本文将介绍在FPGA中构造存储器的方法,特别是结合高速数据采集的特点重点描述双端口RAM的构造方法及其应用。

在FPGA中构造存储器

许多系列的FPGA芯片内嵌了存储阵列,如ALTERA EPlK50芯片内嵌了5K字节的存储阵列。因此,在FPGA中实现各种存储器,如单/双端口RAM、单/双端口ROM、先进先出存储器FIFO等非常方便,而且具有诸多优点。其硬件可编程的特点允许开发人员灵活设定存储器数据的宽度、存储器的大小、读写控制逻辑等,尤其适用于各种特殊存储要求的场合。FPGA/FPGA器件可工作于百兆频率以上,其构造的存储器存取速度也可达百兆次/秒以上,这样构成的高速存储器能够胜任存储数据量不太大,但速度要求很高的工作场合。

FPGA中构造存储器主要有两种方法实现。一是通过硬件描述语言如VHDL、AHDL、Verilog HDL等编程实现。二是调用MAX+PLUSⅡ自带的库函数实现。调用库函数方法构造存储器较硬件描述语言输入方式更为方便、灵活、快捷和可靠,故也更常用之。

利用库函数构造双端口RAM

在MAX+PLUSⅡ中有几个功能单元描述库。prim逻辑元库,包括基本逻辑单元电路,如与、或、非门,触发器、输入、输出引脚等;mf宏功能库,包括TTL数字逻辑单元如74系列芯片;而下文将要详细介绍的参数化双端口RAM模块所在的参数化模块库(mega-lpm)中,包括各种参数化运算模块(加、减、乘、除)、参数化存储模块(单、双端口RAM、ROM、FIFO等)以及参数化计数器、比较器模块等等。库中的这些元件功能逻辑描述经过了优化验证,是数字电路设计中的极好选择。

mega-lpm库中共有五种参数化双端口RAM模块:ALTDPRAM、LPM_RAM_DP、CSDPRAM、LPM_RAM_DQ和LPM_RAM_IO。其中ALTDPRAM和LPM_RAM_DP模块读写有两套总线,读和写有各自的时钟线、地址总线、数据总线和使能端,可同时进行读写操作。除此之外,ALTDPRAM模块还有一个全局清零端口。CSDPRAM模块则有a、b两组写端时钟线、地址总线、数据总线和使能端,可同时对RAM进行写操作,但对RAM读、写只能分时进行。LPM_RAM_DQ模块相对简单,读与写共用一组地址总线,有各自的数据线和时钟线。LPM_RAM_IO模块只有一组地址总线和数据总线。

mega-1pm函数库中的双端口RAM模块全是参数化调用,这为设计带来极大的方便。通过对各种参数的取舍、参数设置和组合,再结合读写控制逻辑就可以构造出设计需要的存储器模块。双端口RAM常见的应用模式主要有以下两种:

1.存储器映像方式。该方式可以随意对存储器的任何单元进行读写操作。其主要应用于多CPU的共享数据存储、数据传送等。该方式中,读、写控制线、地址总线和数据总线有两套。根据两端口之间数据的传送方向为单向或双向,又有单向数据总线和双向数据总线之分。

2.顺序写方式。该方式对RAM的写操作只能顺序写入。这种情况适用于对象特性与时间紧密相关或传送数据与顺序密切相关的场合,如文件传送、时序过程、波形分析等。根据写控制逻辑的不同,可对RAM进行循环写入或一次写入方式。该方式下的读操作可以是存储器映像读或顺序读,前一种有较大的灵活性,而后一种则类似于FIFO形式。

在读、写使用独立的地址总线和数据总线时,可以同时对RAM不同单元进行读写操作。根据不同控制逻辑的要求,对读写时钟、时钟使能端口可以适时设置,以满足控制需要。

下面以LPM_RAM_DP模块为例介绍库函数法构造双端口RAM的步骤。

首先在MAX+PLUSⅡ中建立一个图形编辑文件。双击文件任意空白处弹出库函数选择窗口。然后从mega-lpm库中选择LPM_RAM_DP模块。

在LPM_RAM_DP模块中共有9个可配置参数:

LPM_FILE——指定存储器的初始化数据文件;

LPM_INDATA——选择输入数据采用寄存方式还是非寄存方式;

LPM_NUMWORDS——设置存储器的深度(大小);

LPM_OUTDATA——选择输出数据采用寄存方式还是非寄存方式;

LPM_RDADDRESS_CONTROL——决定读地址控制信号是寄存方式还是非寄存方式;

LPM_WIDTH——设置存储数据宽度;

LPM_WIDTHAD——设置地址总线宽度;

LPM_WRADDRESS_CONTROL——选择写地址控制信号是寄存方式还是非寄存方式;

USE_EAB——决定是否使用嵌入式阵列块。

双击双端口RAM参数列表可弹出引脚/参数设置窗口。在引脚/参数设置窗口可以具体对双端口RAM进行引脚、参数设置。可以根据具体的对存储器的功能要求,决定各种口线的使用与否。例如不想使用rdclken(读时钟使能)信号,则可以将其Status设置为Unused即可。同时还可以通过Inversion项设定该信号的初始状态(初始值)。在窗口的Parameters参数设置处,选择不同的参数项后,通过ParameterValue项可以改变或设置其相应的状态或数值。如想设置存储数据为8位宽度,则选择LPM_WIDTH项,然后将Parameter Value设置为8。

例如要设计一个11位宽数据,512个存储单元,使用读写同步时钟、不需要读写使能端及时钟使能端的双端口RAM。则可以打开引脚/参数设置窗口,设置LPM_NUMWORDS为512,LPM_WIDTH为11,LPM_WIDTHAD为9,LPM_INDATA、LPM_OUTDATA、LPM_RDADDRESS_CONTROL和LPM_WRADDRESS_CONTROL为寄存方式,使用嵌入式阵列;rdaddress、rdclock、data、wraddress、wrclock、q为Used,rden、rdclken、wren、wrclken为Unused。

其它存储器的构造方法

不同的存储器根据各自特点,应用场合也不尽相同。ROM存储器主要用来存储"常量",如系统参数、波形发生器的信源等。先进先出FIFO存储器可用于信号的实时不间断采集,存储、缓冲两个异步时钟之间的数据传输等。

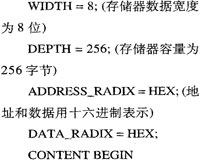

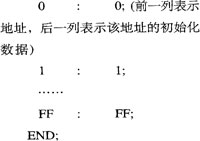

ROM、FIFO等存储器的调用库函数构造方法与双端口RAM的构造方法类似,在mega-lpm库中调用相应的模块单元即可。其中ROM存储器在库中是LPM_ROM模块,FIFO存储器在库中有CSFIFO、DCFIFO、LPM_FIFO、LPM__FIFO_DC、SCFIFO、SFIFO共六种。需要说明的是由于ROM在实际系统运行时的不可写入性,在ROM构造过程中要对ROM存储器进行数据初始化。这一操作是通过设置PLM_FILE项完成的。在引脚/参数设置窗口的Parameters参数设置处选择该项,再通过ParameterValue项确定相应的数据初始化文件(*.mif)即可。下面是VHDL格式的ROM数据初始化文件(文件可用任何文本编辑器实现):

双端口RAM在高速数据采集中的应用

利用传统方法设计的高速数据采集系统由于集成度低、电路复杂,高速运行电路干扰大,电路可靠性低,难以满足高速数据采集工作的要求。应用FPGA可以把数据采集电路中的数据缓存、控制时序逻辑、地址译码、总线接口等电路全部集成进一片芯片中,高集成性增强了系统的稳定性,为高速数据采集提供了理想的解决方案。下面以一个高速数据采集系统为例介绍双端口RAM的应用。

该系统要求实现对频率为5MHz的信号进行采样,系统的计算处理需要对信号进行波形分析,信号采样时间为25μs。根据设计要求,为保证采样波形不失真,A/D采样频率用80MHz,采样精度为8位数据宽度。计算得出存储容量需要2K字节。

根据设计要求,双端口RAM的LPM_WIDTH参数设置为8,LPM_WIDTHAD参数设置为11(211=2048),使用读写使能端及读写时钟。ADCLK、WRCLK和地址发生器的计数频率为80MHz。

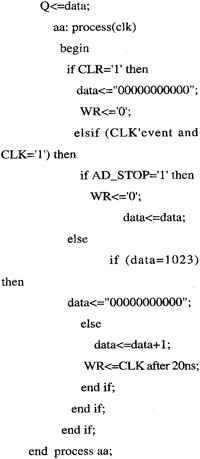

A/D转换值对双端口RAM的写时序为顺序写方式,每完成一次A/D转换,存储一次数据,地址加1指向下一单元,因此写地址发生器(RAM_CONTROL)采用递增计数器实现,计数频率与ADCLK、WRCLK一致以保证数据写入时序的正确性。写操作时序由地址和时钟发生器、A/D转换时钟和双端口RAM的写时钟产生。停止采样时AD_STOP有效,写地址发生器停止计数,同时停止对RAM的写操作。将地址发生器的计数值接至DSP总线可以获取采样的首尾指针。地址发生器单元一般用(VHDL)语言编程实现,然后生成符号文件RAM_CONTROL在上层文件调用。其部分VHDL语言程序如下:

对双端口RAM的读操作采用存储器映像方式,其读出端口接DSP的外扩RAM总线,DSP可随机读取双端口RAM的任一单元数据,以方便波形分析。 由于LPM_RAM_DP模块的读端数据总线q不具有三态特性,因此调用三态缓冲器74244,通过其将输出数据连接到DSP数据总线上。

在高速数据采集电路中,数据缓存也可以用FIFO或单端口RAM实现。用FIFO进行数据缓存,由于其已经把地址发生部分集成在模块单元内,因此省去了一部分程序编写,但是DSP却不能任意地访问FIFO的存储单元,只能是顺序写入/读出数据,这样设计,系统的灵活性就大大降低。如果DSP的分析计算需要特定单元的数据,则系统的效率和速度会因为无效数据的读取而降低。使用单端口RAM进行数据缓存同样存在一些问题。由RAM侧看,DSP和A/D转换器是挂在一条总线上的,当从RAM向DSP传输数据的时候,A/D转换器就不能有数据传到该总线上,否则会产生总线冲突,引起芯片损坏。解决这个问题就需要增加电路。应用双端口RAM就不存在这个问题,而且使系统结构划分更明确,符合模块化设计思想。

结语

综上所述,利用FPGA芯片的高速工作特性,以及其内部集成嵌入式阵列和大规模逻辑阵列的特点,设计存储器,三态缓存器、地址发生器、以及复杂的时序逻辑电路等,应用于高速数据采集电路中可以使电路大大简化,性能提高。同时由于FPGA可实现在系统编程(ISP),使系统具有可在线更新、升级容易等特点,是一种较为理想的系统及电路实现方法。

作者:王建国 吕艳宗 来源:电子设计应用