- 易迪拓培训,专注于微波、射频、天线设计工程师的培养

基于DSP和GC5322的数字预失真系统设计

随着多载波调制技术的发展,调制电平也随之增加。功放的各种线性和非线性失真对无线数据传输性能的影响越来越大。尤其是功放发射峰均比较大时,发射功率变化较大,有时甚至会造成功放的自保护,导致停止发射或者烧毁功放。功放的实际工作曲线不是呈线性变化,而是呈非线性变化,而且不同的功放曲线变化不一致,就是同一个功放在不同工作环境下其曲线也不一致。这样,使得无法使用一种通用的算法公式校正功放的工作曲线。为此,提出功放预失真技术,校正功放的非线性工作曲线,使得实际发射功率稳定。

数字预失真技术目前已经在软件实现上得到了初步的发展。目前一般的预失真技术采用软件架构,使用数字信号处理器采集功放功率值,并分析其变化曲线,形成数据表格,并存储。在以后的发射之前根据存储的表格数据对发射功率进行预校正。该方法在实际工作中由于电磁环境变化、温度变化、功放元器件老化、晶体频率飘移等影响,使得预校正数据和真实校正数据存在较大的偏差,从而影响校正效果,甚至向反方向校正情况。软件校正形成校正数据需要较长的时间,一般为几十秒以上,使得实时校正难以实现。这样使得软件数字预失真技术的实用性降低,适用场合减少。

本文提出一种基于硬件的数字预失真校正系统的设计方法。采用TI公司的数字信号处理器DSP芯片C6727B和专用的数字预失真芯片GC5322实现预失真系统。文中重点介绍DSP和GC5322的软硬件连接。硬件数字预失真系统由专用器件实现预失真处理,解决预失真的实时性问题;此外,进行预失真系统设计时,只需要实现对硬件芯片的配置,而无须编写复杂的算法,简化实现难度。

预失真技术和GC5322

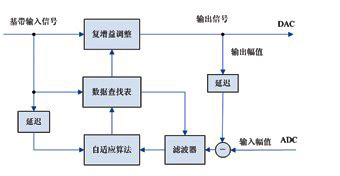

数字预失真(DPD,Digital Pre-Distortion)的工作原理就是预先产生非线性失真分量,去抵消功放中产生的非线性产物。一般的中频预失真和射频预失真,都是以发射系统最终输出信号的三阶交调功率比来衡量其性能指标。和模拟预失真以及前馈架构相比,数字预失真在提高效率、多载波应用、修正效果以及自适应方面具有很大的优势。对于零中频架构的无线信号收发系统,数字预失真在修正零中频架构中的本振泄漏和镜像抑制方面, 具有非常好的效果。功放预失真示意图如图1所示。

图1 预失真示意图

数字预失真系统的构成框图如图2所示。基带输入信号和存储在数据查找表的预失真数据经过复增益调整模块处理,处理后的数据从DAC发送出去,完成预失真处理。同时,ADC开始采样发射数据,得到当前发射信号的功率值,经过滤波器去抖动和噪声后,送入自适应算法模块,自适应算法模块综合基带输入信号和实际发射出去的信号,得到新的预失真数据,并存储到数据查找表中,从而完成实时的功放工作曲线校正。

从图2中可以看出,预失真工作需要实时ADC采样,并实时处理数据。工作量较大,由于一般的处理系统不能实时处理,只能在发射真实信号前,预先发射测试数据,生成数据查找表,以后则以此表格数据修正功放工作曲线。显然,这种方法很难实现实时处理,为了解决实时修正问题,TI公司推出GC5322预失真处理芯片。

图2 数字预失真系统构成

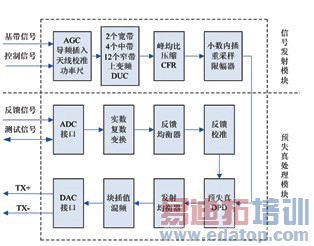

GC5322的内部结构如图3所示。信号发射模块主要包括自动增益控制(AGC,Adaptive Gain Control)、导频插入(Pilot Insertion)、功率尺(Power Meter)、峰均比压缩(CFR,Crest Factor Reduction)、小数内插重采样(FFR,Fractional Farrow Re-sampler)以及限幅器(Circular Limiter)等模块。发射模块可以实现2个宽带信号,例如2个10MHz带宽的OFDMA信道;或者实现4个中带信号,例如4个5MHz带宽的WCDMA载波;或者实现12个窄带信号,例如12个CDMA2000/TDSCDMA载波。

图3 GC5322的内部结构

预失真模块是GC5322的最重要功能。该模块的主要单元包括ADC/DAC接口、实数复数变换、带反馈环的均衡器和校准器、预失真处理模块、发射均衡器和混频器等。

ADC转换器采集功放输出信号,转换成数字信号并变换后成为反馈信号进入反馈环节;反馈信号经过一系列的下变频处理,包括增益调整、频率和相位归一化处理等。其中还使用一个8阶的反馈均衡器实现射频到中频的失真校正。

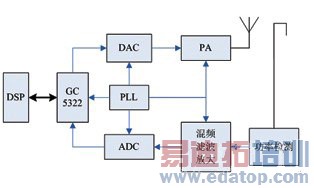

系统硬件结构

系统以数字信号处理器DSP芯片C6727B为核心单元,实现对整个过程的控制。C6727B是TI公司在C671x基础上发展的浮点型DSP,其最高工作频率达到350MHz。单个指令周期可以执行6个浮点数据运算,最高达到2100MFLOPS;片内具有256KB的RAM;片内外设有EMIF、UHPI、音频接口、dMAX、定时器以及IIC、SPI等接口。完全满足对GC5322控制的要求。整个系统硬件结构如图4所示。

图4中,PLL模块提供一个统一的时钟信号到各个单元,尤其是GC5322、ADC、DAC以及功放和滤波放大电路需要统一的时钟,否则系统预失真效果变差。C6727B和GC5322的连接是系统的重点,其硬件连接如图5所示。

图4 系统硬件结构

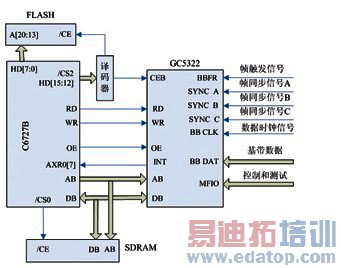

图5中使用C6727B的EMIF接口连接到GC5322的数据和地址总线,同时EMIF接口的总线还连接到系统中的SDRAM和FLASH存储芯片。SDRAM是为了存储DSP程序运行产生的中间变量;FLASH存储程序,上电开始过程中由DSP读取。此外,FLASH还可以存储掉电不丢失的数据,例如预失真校正数据。由于C6727B的EMIF接口只有两个片选信号,其中CS0是专门用于SDRAM的选通信号,CS1统一给所有的异步外设,包括FLASH和GC5322。为此,使用译码电路完成多个异步外设的选择,使用CPLD或者FPGA完成。GC5322的中断信号必须连接到DSP,由于C6727B没有专用的中断信号,为此使用C6727B的音频串口的AXR0作为通用IO引脚,并配置成中断信号。

图5 C6727B和GC5322的连接

系统软件设计

系统软件设计主要包括GC5322的初始化、DSP的初始化、EMIF接口设置、中断使能、ADC/DAC设置等。系统初始化后,DSP判断当前是否有数据需要发送,数据的读写通过判断是否有挂起的中断,该中断由GC5322产生,一旦GC5322收到基带数据,将发出该中断。无数据读写情况下,DSP将定期检测GC5322的测试信号,以便确定GC5322在正常工作。也可以根据需要,将GC5322设置到低功耗状态。

如果GC5322开始工作,则启动ADC开始采样,并控制时序将ADC采样后数据传输到GC5322,GC5322根据设置进行预失真处理,从而校正DAC的输出幅度,完成预失真处理。

作者:张运安 付河 来源:《今日电子》

我推荐大家读

轻松参与

VS

表达立场

这是垃圾文章

上一篇:基于ARM的汽车“黑匣子”设计

下一篇:基于ARM的智能来电显示器的设计