- 易迪拓培训,专注于微波、射频、天线设计工程师的培养

基于ADSP21160的数字信号处理系统设计

摘要:本文使用ADSP21160芯片作为测量运动到达方向平台的主处理器,构建数字信号处理系统,用于信号的二维DOA估计的矩阵运算。

引言

利用阵列信号进行信号的二维到达方向(DOA)估计是近些年来研究的热点。现在,DOA估计虽然已经达到相当高的精度,但由于要进行大量的矩阵运算,必然要耗费一定的时间。在某些情况下,为保证系统的实时性,对系统的硬件的运算速度提出了一定的要求。此时,应用高端的DSP通用芯片进行数据处理是一个不错的选择。本文使用ADI公司的ADSP21160为主处理器搭建了信号处理硬件平台,给出了对系统的构思及具体电路设计,具有一定的实用价值。

ADSP21160采用超级哈佛结构,片内有4套独立的总线,分别用于双数据存取、指令存取和输入/输出接口,片内集成了处理器核(包括运算单元、控制单元、地址产生器和总线、中断、寄存器等)、大容量双端口静态存储器、程序/数据外部总线及多处理器接口、输入/输出控制器等数字信息处理系统的主要功能块。

硬件系统的设计思路

下面从数据的输入输出,系统的上电运行,系统的电源配置及电路控制等方面简单介绍系统的设计思路。

1.首先考虑数据传输。外部设备(接收机)通过50针接口将数据经ADSP21160处理后转换成串行数据输出,传递给外设(控制器)及计算机。为了电路系统的保密性以及便于系统中一些逻辑控制电路的实现,在ADSP21160和50针接口之间增加了一个CPLD控制电路。

2.为了上电后系统可以自行运行,需要给DSP配置一个外接FLASH,并将计算程序预先烧写FLASH中。通过配置ADSP21160的引导方式,系统上电后,ADSP21160可自动从FLASH中读取程序并运行。

3.由于ADSP21160只有4Mbit的内部存储空间,且等分为数据存储空间和程序存储空间两部分。为了系统及程序今后升级的方便,使用SRAM配置了512K×32位的外部存储空间。

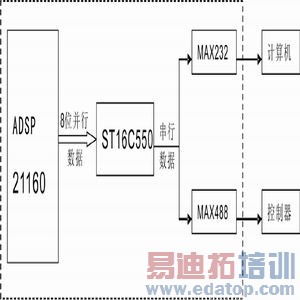

4.由于ADSP21160的串行口不是通用的UART串口,而系统和计算机均要求串行数据输出,故系统中需要一个并串转换芯片来输出运算结果。

5.由于外部只提供+5V直流电源,而ADSP21160要求+3.3V的接口电源及2.5V的内核电源,故系统内部器件也相应的尽量选择+3.3V器件,故系统需要一个DC/DC转换芯片将+5V电源转换成+2.5V及+3.3V的电源输出。

系统的各功能模块设计

电源模块设计

在系统的设计中,由于ADSP21160的外部接口电源是+3.3V,故为了简化电路及提高电路板的性能,在其他器件的选择上,也尽量选择了+3.3V器件。少数难以找到+3.3V电源的器件,在不影响接口及功能的情况下,选择了+5V器件。另外ADSP21160还要求+2.5V的内核电源及+2.5V的模拟电源(供ADSP21160的内部锁相环使用)。而外部给系统提供的是+5V的电源。综合以上要求考虑,系统需要一个DC/DC转换模块,输出+3.3V及+2.5V电压,并将+2.5V电源分成数字及模拟两路。

ADSP21160要求内核电源供电早于外部口供电,否则可能导致DSP启动异常或程序无法加载。故在电源设计中考虑到这个问题,决定使用DC/DC的+2.5V输出端经过延时电路接到+3.3V输出使能端,很好的解决了这个问题。

综合系统对电压和电流的具体要求,本硬件系统选择了TI公司的TPS767D301作为DC/DC转换芯片。其输入为+5V电压,输出一路+3.3V电压及一路+1.8V或+2.5V可调电压,电流最大输出为1A。

DSP主模块设计

时钟驱动:ADSP21160需要外部时钟驱动,故外接时钟是必不可少的。其内部特有的锁相环设置可以将内部的运算频率倍频至外部时钟频率的2、3或4倍,最高的核时钟频率为80MHz。这样,就可以在外部频率(数据传输频率)较低的情况下,实现内核处理器的高速运行。

在本系统中,为了提高系统的高频炕干扰能力及降低系统的设计难度,在对系统运行速度影响不大的情况下(由于系统的主要耗时集中在矩阵的处理运算上,数据传输相对而言只占其全部运行时间的几十分之一),外部选择了20MHz的驱动时钟,再设置内部锁相环为外部时钟的4倍,实现其内部的高速运算。

程序加载:ADSP21160需要外接一个14针的JTAG接口,通过使用ADI公司提供的ICE仿真器,从计算机下载编制好的用户程序,装入ADSP21160的内部存储器或外接FLASH中。

外部器件选通:ADSP21160配置了/MS3~/MS0四个外部引脚,用于外部器件的选通。在同一时间,只其中允许一个有效(低电平)。这些引脚分别连接于FLASH、SRAM、并串转换芯片(ST16C550)的使能端,用于选通这些部件以及用于与外部接收机的数据通信。CPLD由于关系到数个器件的逻辑功能,故长期处于工作状态(使能端直接接地)。

FLASH加载及外扩存储器模块设计

FLASH加载模块:为了系统能够在上电后自动运行,为ADSP21160配置了外接FLASH。按照ADSP21160的用户手册,8位FLASH的数据线接DSP数据线的32_39位,地址线必须从ADDR0开始与ADSP21160相应地地址位直接连接。ADSP21160采用EPROM启动模式,用/BMS和/MS0相与后连接于FLASH的使能端。

图1 系统的整体框图

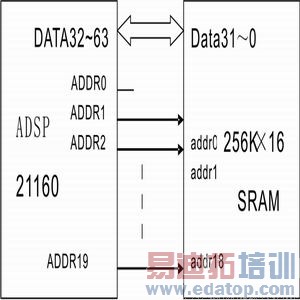

外扩存储器模块:ADSP21160是高性能的32位浮点处理器,对外最多可使用64位的数据总线。考虑到系统的精度要求及内部数据的处理模式,本系统对外只使用了32位的数据总线。这样,在外扩存储器的选择上,考虑到价格等因素,选用了两块256K×16位的SRAM并联构成32位的外扩存储器,如图2所示。

图2 ADSP21160与SRAM的连接

在地址线的连接上,和一般的接法梢有不同。由于ADSP21160规定,对外部空间的寻址,其奇地址通过低32位数据线传递;偶地址通过高32位数据线传递。考虑到在FLASH的连接上使用了DSP数据线的32_39位,为了简化今后PCB板的布线及充分利用SRAM的存储空间,在设计中,将ADSP21160的ADDR0的引脚悬空,将其ADDR1引脚与SRAM的addr0管脚相连,ADDR2与addr1相连,以下顺次连接。

外部通信接口模块设计

目标板通过一个50针接口与接收机相连,通过RD_REQ、RD_PMT、RD_EN、RD_CLK四根控制信号线进行,从接收机内部开辟的存储空间读取数据。

在本系统的设计中,其中间运算数据均采用32位浮点数,输出结果截取8位有效数字,通过并串转换器(ST16C550)转换成串行数据,再分成两路,一路经过MAX488转换成差分数据输送的外部控制器,另一路经过MAX232转换电平,连接到计算机,实现了系统要求的功能,如图3所示。

图3 ADSP21160的数据输出

结语

ADSP21160功能强大,但在电源配置上稍显复杂。本系统利用2.5V电源输出作为3.3V的输出使能,成功的解决了这一问题。另外,在达到系统要求的基础上,为降低设计难度,对时钟和数据线都进行了特殊的设计。时钟采用片外中低频(20MHz),片内倍频到最大频率(80MHz)的设计,降低了PCB板对中高频布线要求;数据线通过悬空0位地址,将片外线宽从64位降低至32位,大大降低了ADSP21160周边的线密度,从而大大降低了PCB板的布线难度。

参考文献:

[1] ADSP-21160 SHARC DSP Hardware Reference,Analog Device Inc.

[2] ADSP-21160 SHARC DSP Instruction Set Reference,Analog Device Inc.

[3] ADSP-21160M Data Sheet,Analog Device Inc.

[4] 苏涛,吴顺君,李真芳,宋万杰,高性能DSP与高速实时信号处理,西安电子科技大学出版社

[5] 苏涛,蔡建隆,何学辉,DSP接口电路设计与编程,西安电子科技大学出版社

[6] 刘书明,罗军辉,ADSP SHARC系列DSP应用系统设计,电子工业出版社

作者:沈逢春 钟洪声 电子科技大学电子工程系 来源:《电子产品世界》2005年09期

我推荐大家读

轻松参与

VS

表达立场

这是垃圾文章