- 易迪拓培训,专注于微波、射频、天线设计工程师的培养

Virtex-6 HXT FPGA ML630:光传输网络评估方案

Xilinx公司的Virtex-6 FPGA包括Virtex-6 LXT FPGA,Virtex-6 SXT FPGA和Virtex-6 HXT FPGA三个亚系列,采用40nm ExpressFabric和600MHz Clocking技术,具有存储器选择如能和DDR3,QDRII+和RDLRAM存储器接口,600MHz DSP48E1 Slice,高速互连性,以太网媒体接入控制器具有10/100/1000Mbps,同时具有系统监视器和ADC,增强性配置和比特流保护,广泛用在有线通信,无线通信和广播设备。

Virtex-6 FPGA是目标设计平台的可编程的芯片基础,这一平台提供了集成的软件和硬件产品,从而使设计者可以从他们开发周期的初始阶段就专注于创新。采用第三代ASMBL(高级芯片模块时钟)圆柱型架构,Virtex-6包含了多个不同的子系列。这份简介涵盖了LXT、SXT和HXT子系列中的器件。每个子系列都包括不同比率的特性,以便高效的满足各种高级逻辑设计的需求。除了高性能逻辑构造外,Virtex-6 FPGA还包括许多内置的系统级模块。这些特性使设计者可以在其采用FPGA的系统中,构建高等级的性能和功能。利用先进的40nm铜工艺技术,Virtex-6 FPGA成为传统ASIC技术的可编程替代产品。Virtex-6 FPGA提供了较佳的解决方案,可通用前所未有的逻辑、DSP、连接性和软件微处理性能,满足高性能逻辑设计者、高性能DSP设计者、高性能嵌入式系统设计者的需求。

Virtex-6 FPGA主要特性

·三个子系列

·Virtex-6 LXT FPGA:带有高级串行连接的高性能逻辑

·Virtex-6 SXT FPGA:利用高级串行连接性,实现较高的信号处理性能

·Virtex-6 HXT FPGA:较高的带宽串行连接性

·子系列之间具有兼容性

·LXT和SXT器件在相同的封装上点位布局相同

·高级、高性能FPGA逻辑

·真正的6输入查找表(LUT)技术

·双LUT5(5输入LUT)选项

·对于需要丰富的寄存器混合的应用,提供LUT/双flip-flop对

·提高了布线效率

·每个6输入LUT上的64位(或两个32位)分布式LUT RAM选项

·带有寄存器输出选项的SRL32/串行SRL16

·强大的混合模式时钟管理器(MMCM)

·MMCM模拟提供了零延迟缓冲、频率合成、时钟相移、输入抖动过滤和相位匹配时钟分配

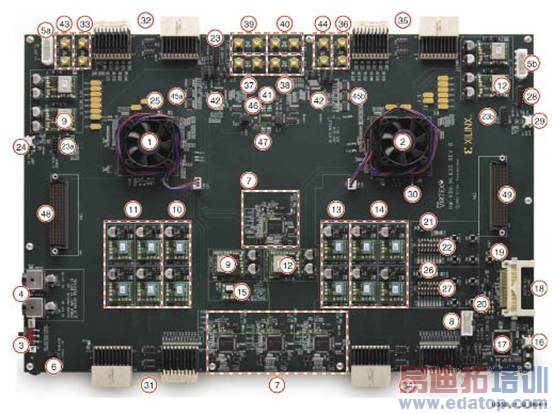

图1 ML630光传输网络(OTN)外形图

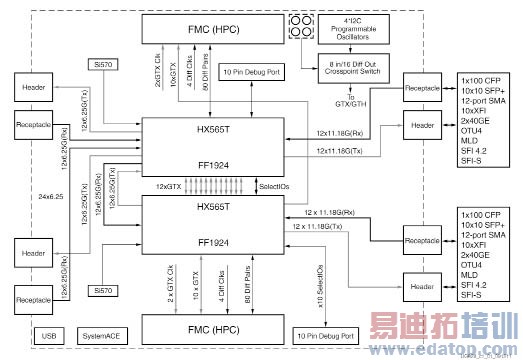

图2 ML630光传输网络(OTN)方框图

·36kbits时钟RAM/FIFO

·双端口RAM模块

·可编程

-高达36位的双端口带宽

-高达72位的简易双端口带宽

·增强型的可编程FIFO逻辑

·内置可选的校错电路

·可选择采用将每个模块用作两个独立的18kB模块

·高性能并行SelectIO技术

·1.2V~2.5V I/O的工作电压

·采用ChipSync技术的源同步接口技术

·数字控制阻抗(DCI)的活动终端

·灵活的精密型I/O

·具有集成写入测量性能的高速存储接口

·高级DSP48E1片

·25×18、两种补充的乘法器/加法器

·可选的流水线操作

·新的可选预加法器,辅助过滤应用

·可选的按位逻辑功能

·专用的级联连接

·灵活的配置选项

·SPI和并行闪存接口

·利用专用低效运行再配置的支持多数据流

·自动总线带宽检测

·所有器件上的系统监视器性能

·片上/片下热监视和电源电压监视

·JTAG访问所有的受影视数量

·适用于PCI Express设计的集成型接口模块

·符合PCI Express Base

Specification 2.0

·利用GTX收发器,支持Gen1 (2.5 Gbits/s)和Gen2 (5 Gbits/s)支持

·具有端点和下游端口

·每个模块上的×1,×2,×4或×8 lane支持

·GTX收发器:高达6.6 Gbits/s

·通过FPGA逻辑中的采样过密支持低于480Mbits/s的数据率

·GTH收发器:2.488 Gbits/s到高于11Gbits/s

·集成型10/100/1000 Mbits/s以太网MAC模块

·采用GTX收发器,支持1000BASE-X PCS/PMA和SGMII

·采用SelectIO 技术资源支持MII、GMII和RGMII es

·可支持2500Mbits/s

·40nm铜CMOS工艺技术

·1.0V内核电压 (仅-1,-2,-3速度级)

·低功耗 0.9V内核电压选项 (仅-1L速度级)

·可采用独立或无铅封装选项的高信号集成倒装芯片封装ML630光传输网络(OTN)评估板主要特性

·两个Virtex-6 XC6VHX565T-2FFG1924C FPGA

·采用功率状态LED实现所有需要电压的板上稳压器

·所有 ML630 FPGA U1和U2 I/O 块VCCO电压为2.5V

·两类外部电源插座 (12V "砖块" DIN4(典型值),PC ATX(典型值))

·USB JTAG配置端口,与 USB A-to-Mini-B线缆一起使用

·系统ACE控制器,带有同伴CompactFlash插槽

·适用于每种FPGA的通用型按钮和DIP开关、LED和测试I/O头

·用于每种FPGA的VGA 2X5 male调试头

·用于每种FPGA,采用USB Mini pcb连接器的USB-至-UART桥

·两个VITA 57.1 FMC HPC连接器

·I2C总线集合EEPROM,时钟源和FMC连接器

·一个单独的 SiTime,固定200 MHz 2.5V LVDS振荡器绕线至每个FPGA整体时钟输入

·8对差分时钟输入SMA连接器

·六个I2C 可编程Silicon Labs Si570 3.3V LVPECL 10 MHz至810 MHz 振荡器

·两种不同输入8×8交叉形式关,提供16个可选的差分时钟源

·四套插座FCI Airmax 120引脚连接器,采用Interlaken互连协议

详情请见:

http://solution.eccn.com/solution_2012012911035421.htm

来源:《世界电子元器件》

上一篇:FTTH网络的建设部署特点分析

下一篇:未来大容量数据网络的关键设备—光交换机