- 易迪拓培训,专注于微波、射频、天线设计工程师的培养

基于ARM-WinCE平台的时钟同步设计

摘要:时钟同步是分布式系统的核心技术之一,为实现基于ARM-WinCE嵌入式系统平台的测试仪器组建分布式测试系统,在介绍IEEE1588精确时钟协议基本原理的基础上,提出了使用具有IEEE1588协议硬件支持功能的DP83640以太网物理层收发器在基于ARM-WinCE的嵌入式系统平台上实现时钟同步的设计方案,给出了硬件设计的接口电路和软件设计框架。经测试该方案可达到不低于1μs的同步精度。

随着计算机技术、网络通信技术的进步,组建分布式网络化测试系统,提高测试效率、共享信息资源,已成为现代测试系统发展的方向。分布式测试系统通过网络等通信媒介把分布于各测试点、独立完成特定功能的测试设备连接起来,以达到测试资源共享和协同工作等目的。时钟同步是分布式系统的核心技术之一,其目的是维护一个全局一致的物理或逻辑时钟,使得系统内各个节点中与时间有关的信息、事件及行为有一个全局一致的解释。IEEE1588精确时钟协议是当前分布式测试系统中时钟同步研究的热点。采用硬件支持的IEEE1588协议能够在以太网中不同结点之间实现纳秒级的时钟同步,为工厂自动化、测试和测量以及通信等领域需要高精度时钟同步的应用提供了一种有效的解决方案。本文采用具有IEEE1588精确时钟协议硬件支持功能DP83640芯片在基于ARM和WinCE的嵌入式系统平台上实现IEEE1588协议,为基于嵌入式系统的智能测试仪器组成分布式测试系统奠定了基础。

1 IEEE1588协议原理

IEEE1588的全称是"网络测量和控制系统的精密时钟同步协议标准",简称精确时钟协议(PrecisiON Time Protocol,PIP)。IEEE1588协议是通用的提升网络系统定时同步能力的规范,在起草过程中主要参考以太网来编制,使分布式通信网络能够具有严格的定时同步,并且应用于工业自动化系统。基本构思是通过硬件和软件将网络设备(客户机)的内时钟与主控机的主时钟实现同步,提供同步建立时间小于10μs的运用,与未执行IEEE1588协议的以太网延迟时间1000μs相比,整个网络的定时同步指标有显着的改善。

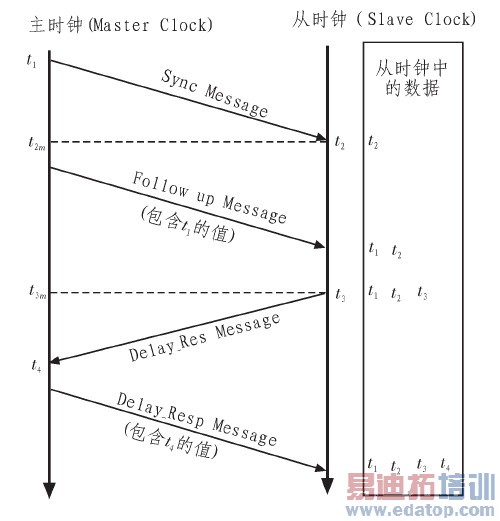

IEEE1588时钟协议在进行时钟同步时,主时钟设备按照一定的时间间隔(一般为2 s)周期性地以广播方式发送同步报文(Sync)和同步跟随报文(FollowUp),且在FollowUp报文中记录Sync报文的发送时间戳t1,而从时钟设备接收Syne报文记录接收时间戳为t2;然后,从时钟设备节点定期发送延迟请求报文(Delay_Req)(一般4~60 s发送一次),并记录其发送时间戳t3,主时钟设备接收判延迟请求后,记录接收时间戳t4,并给相应从节点发送延迟请求响应报文(Delay_Resp),该报文信息中包古时间戳t4.通过得到的4个时间戳,可以计算出主从时钟之间的偏移量Toffset和网络传输的线路延迟ms_delay,其过程如图1所示。

图1 时钟同步过程

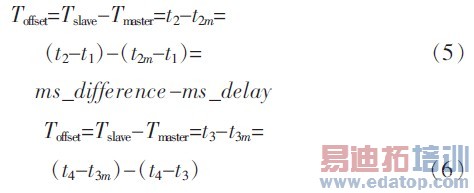

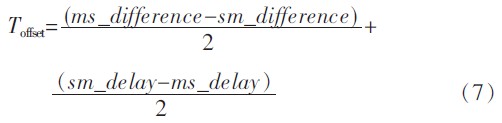

Sync报文在主从设备的时差为:

Delay_Req报文在主从设备的时差为:

Sync报文传送时主从设备的线路延迟为:

Delay_Req报文传送时主从设备线路延迟为:

Toffest 可以分别用t2-t2m 和t3-t3m表示:

由(5)+(6)得:

由(5)-(6)得:

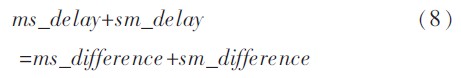

在线路对称的情况下,有:

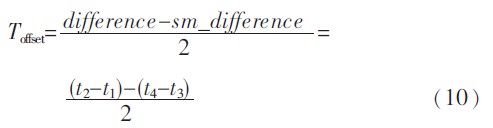

偏移量:

线路延迟:

得到了从时钟与主时钟之间的时间偏移值,就可以采用适当的调节算法来调节从时钟,最终使得从时钟与主时钟同步。从时钟并不是每个同步周期都需要进行时间同步,而是根据从时钟与主时钟之间的时间偏移值等时间信息来决定是否需要进行时间同步。当主从时钟之间建立起稳定的同步关系后,从时钟还需周期性地监听来自主时钟发布的Sync报文,一旦出现主从时钟之间不处于时间同步的状态,就重新进行上述的时间同步过程,直到重新达到主从时钟之间的时间同步。

IEEE1588协议的运行是由时间戳驱动的,时钟同步精度主要归结为时间戳的定时精度。IEEE1588使用UDP协议发送网络同步报文,基于UDP协议传输的过程都是在TCP/IP协议模型下进行数据包的逐层封装和传递的。要使时钟获得的报文发送时间和报文接收时间相对精确、稳定,且把发送延迟和接收延迟不相等这种因素对计算传播延迟产生的影响减小到最低,最好的解决办法就是在TCP/IP协议栈的底层即物理层对同步报文标记时间戳,标记时间戳的操作越接近物理层,计算得到的主从时钟的时间偏移量和传播线路延迟就越准确。要实现这一目的就必须加入专门的硬件设备。美国国家半导体公司(National Semiconductor)推出的DP83640芯片就是一款集成IEEE1588精确时钟协议硬件支持功能的以太网收发器。芯片内置高精度IEEE1588时钟,并具有由硬件执行的时间戳标记功能,可为接收及发送信息包加入时间标记。采用DP83640的同步系统,可获得纳秒级的同步精度。

2 硬件设计

由于IEEE1588协议运行于以太网,在基于ARM的嵌入式系统上采用DP83640芯片移植IEEE1588协议的硬件基确是为系统增加以太网接口电路。以太网接口电路主要由媒体访问控制(Medium Access Control,MAC)器和物理层(Physical Layer,PHY)收发器两部分构成。MAC控制器芯片实现OSI模型数据链路层的功能,提供寻址机构、数据帧的构建、数据差错检查、传送控制、向网络层提供标准的数据接口等功能。PHY芯片实现OSI模型物理层的功能,定义了数据传送与接收所需要的电与光信号、线路状态、时钟基准、数据编码和电路等,并向数据链路层设备提供标准接口。ARM处理器、MAC芯片与PHY芯片三者之间的关系是MAC芯片向上通过其处理器接口(Processor Interface)与ARM处理器的高级外设总线(APB)连接,向下通过其媒体独立接口(Media Independent Interface,MII)接口与PHY芯片连接。最终,PHY芯片与RJ45接口连接。

本文使用SAMSUNG公司的S3C2440A型ARM处理器,其内部设有集成MAC控制器,而DP83640芯片只是PHY收发器,因此二者之间还需要增加MAC芯片。由于目前常用的以太网控制器都集成了MAC控制器和PHY收发器,这里选用DAVICOM公司的DM9000以太网芯片,其特点是:具有MII接口可以和片外PHY芯片连接;寄存器操作简单有效;成本低廉。

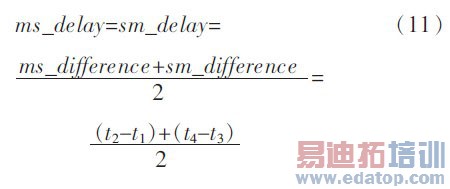

实现S3C2440A与DM9000连接,必须对两者间的数据、地址、控制三大总线进行连接和转换,其连接关系如图2所示。

图2 以太网接口电路

S3C2440A的数据线D[15:0]与DM9000的地址、数据复用数据线SD[15:0]连接用来实现S3C2440A与DM9000之间的数据传输。芯片选择信号AEN与S3C2440A的片选使能信号nGSC4连接,当访问0x20000000-0x27FF FFFF这个范围的地址时会激活片选使能信号nGCS4.DM9000默认I/O基地址为300H.CMD引脚用于设置COMMAND模式,与S3C2440A的ADDR2连接CMD为高电平时,选择数据端口。CMD为低电平时,选地址端口。数据端口和地址端口的地址码由下式决定:

DM9000地址端口=高位片选地址+300H+0H

DM9000数据端口=高位片选地址+300H+4H

高位片选地址由S3C2440A芯片的nGCS4提供,即为:0x20000000.因此DM9000的地址IO基址为0x20000000,数据IO基址为0x2000 0004.向地址IO写数据时不会激活ADDR2,CMD为低电平,所以向DM9000传送的数据为地址,而向数据IO写数据时会激活ADDR2,CMD为高电平,向DM9000传送的数据为数据。S3C2440的输出使能引脚nOE连接DM9000的读引脚IOR,写使能引脚nWE连接DM9000的写引脚IOW.DM9000的中断请求引脚INT连接S3C2440的外部中断请求引脚EINT7,使得S3C2440A能够响应DM9000的中断。

DM9000与DP83640之间通过标准MII接口连接,RXD[3:0]为接收数据线,TXD[3.0]为发送数据线,CRS为载波检测信号,COL为冲突检测信号,RX_DV为数据有效信号,RX_ER为接收错误信号,RX_CLK为接收时钟信号,TX_CLK为发送时钟信号,TX_EN为发送使能信号,MDIO是管理数据的输入输出双向接口,MDC为管理数据接口提供时钟信号。需要注意的是DM9000默认使用片内PHY,因此在驱动程序初始化DM9000时,必须主动置位网络控制寄存器NCR的EXT_PHY位以选择使用片外PHY即DP83640.

3 软件设计

软件设计分为两个步骤:1)是基于DM9000和DP83640进行以太网通信的驱动程序设计;2)是通过DP83640进行时钟同步的应用程序设计。

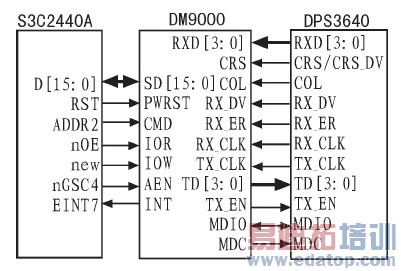

本文使用WinCE5.0操作系统,WinCE5.0系统下网络驱动程序的编写必须符合网络驱动接口规范NDIS(Network Driver Interface Stan dard)。NDIS的层次结构如图3所示,其中最上层的Winsock是提供给应用层的接口。NDIS位于协议驱动层下面,硬件驱动Miniport Driver之上。协议驱动层通过调用NDIS封装的接口函数,实现与底层硬件驱动的交互。WinCE下网络驱动程序的设计主要是在NDIS构架下,针对实际的硬件编写代码,实现相应的中间层Miniport Driver接口函数。其主要完成的功能有:DM9000与DP83640的初始化;网络数据包的发送;网络数据的接收和中断。

图3 NDIS层次结构

实现了以太网通信的驱动程序的基础上,用于时钟同步功能的应用程序通过UDP协议发送、接收时钟同步报文,并进行加入、提取和解析时间戳等操作,这些操作通过读写DP83640内部的1588基本寄存器组(PTP 1588 BASEREGISTERS)和1588配置寄存器组(PIP 1588CONFIGURATION REGISTERS)完成。

4 结论

IEEE1588协议通过在以太网上发送和接收同步报文来实现时钟同步,同步的精度取决于记录报文发送和接收时间的时间戳的精度,因此要实现高精度的时钟同步必须通过硬件支持在通信协议的底层加入和提取时间戳。本文通过在ARM-WinCE嵌入式系统平台上设计了使用DP836 40芯片作为PHY收发器的以太网接口电路及其驱动程序,实现了IEEE1588协议在ARM-WinCE平台上的移植,并达到了不低于1 μs的同步精度,为基于ARM-WinCE平台的测试仪器组建分布式测试系统奠定了基础。

作者:周飞 栾军英 杨通强 赵金辉 来源:《电子设计工程》