- 易迪拓培训,专注于微波、射频、天线设计工程师的培养

基于PSoC3 UDB的异步SRAM读写控制

1 概述

Cypress PSoC3使用基于单循环流水线的高性能8051内核 (67MHz/33MIPS),提供业界广泛采用的5.5V至0.5V电压范围和低至200nA的休眠电流,可以满足极低功耗的应用场合。PSoC3的高性能模拟子系统和数字系统都拥有可编程通路,允许将任何模拟或数字信号(包括可编程时钟)分配到任何通用I/O引脚,这为使用者提供了真正的"系统级"可编程能力。

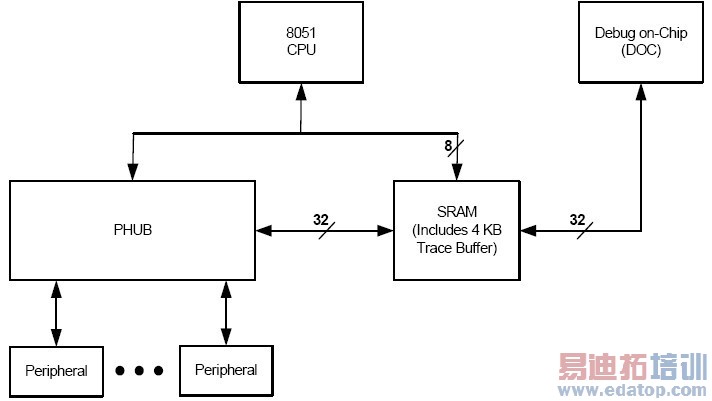

PSoC3中SRAM的容量最大为12KB(3个4KB块),8051CPU和DMA控制器均可访问SRAM.如果访问不同的4KB块,8051和DMA控制器可同时访问SRAM.图1为PSoC3访问片上SRAM框图。

图1,PSoC3访问片上SRAM

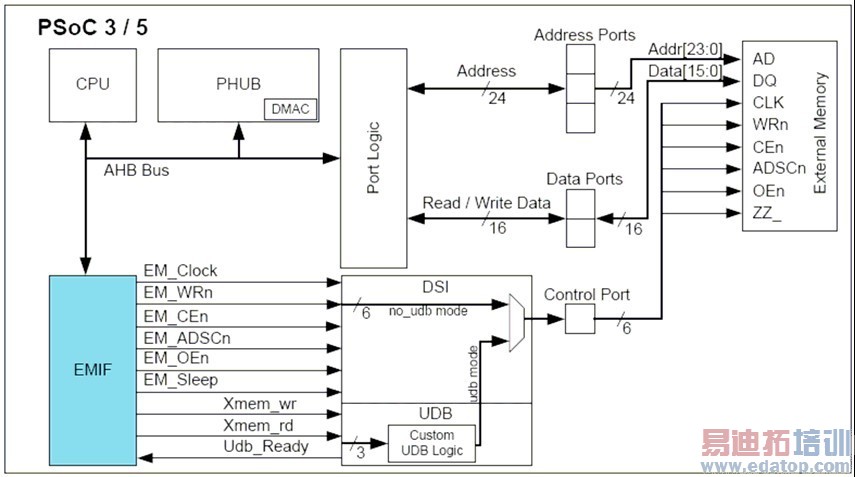

PSoC3同时也提供了外部存储器接口(External Memory Interface, EMIF)用来连接外部的存储器设备。它与UDB、I/O端口和其他硬件产生外部存储器地址和控制信号。EMIF支持同步和异步存储器,但在同一时刻只支持一种存储器类型。其结构如图2所示。

图2,EMIF结构框图

从图2可以看出,CPU和DMAC都可访问SRAM.若数据来源于其他外设比如ADC或者UDB,则数据传输到SRAM的速度将受到CPU或DMAC的限制。因此,在这些数据来源于外设并有传输速度要求的应用中,若采用EMIF可能无法满足其要求。这时可用PSoC3的UDB实现SRAM的读写控制,以实现与外设数据直连。

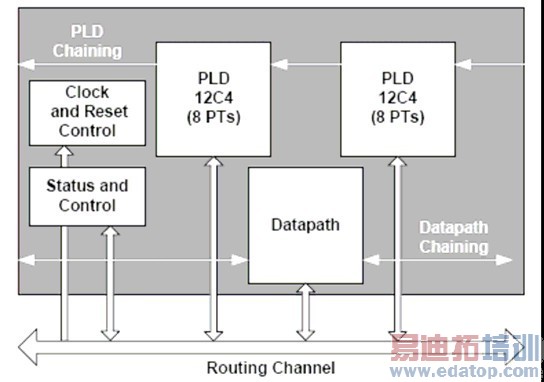

UDB(Universal Digital Blocks)是PSoC3可编程数字系统的核心功能,由可编程逻辑PLD、结构逻辑(Data path)和灵活的布线资源提供在这些元件、I/O连接和其他外设之间的互联,可以创建各种通用外设和定制化功能。PSoC3的数字逻辑部分由多个UDB通过矩阵和可编程互联组成,UDB结构如图3所示。

图3, UDB结构示意图

2 SRAM接口模块设计

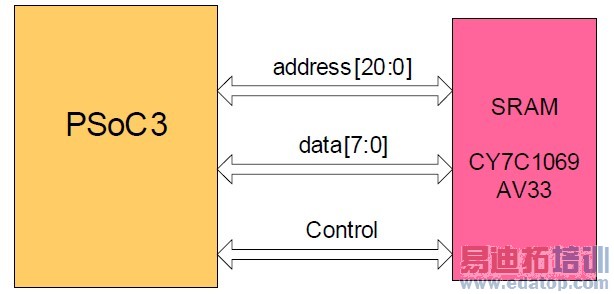

采用PSoC3的UDB 实现对SRAM的读写,就是在PSoC3的UDB中,用Verilog语言设计PSoC3的端口时序以满足SRAM读写的要求,下面以CyprESS的SRAM CY7C1069AV33为例介绍PSoC3 SRAM接口的设计过程。

1) PSoC3 与CY7C1069AV33的硬件连接。

PSoC3与CY7C1069AV33的硬件连接框图如图4所示:

图4,硬件连接框图

PSoC3的具体引脚分配如表一所示:

表一,PSoC3 SRAM控制引脚分配

2) CY7C1069AV33读写时序。

CY7C1069AV33是Cypress生产的2M Bytes 8Bit位宽的高速异步SRAM,支持高速的随机读写操作。它有21根地址线A0~A20,8根数据线D0~D7以及一些控制信号线CE1、CE2、WE和OE.

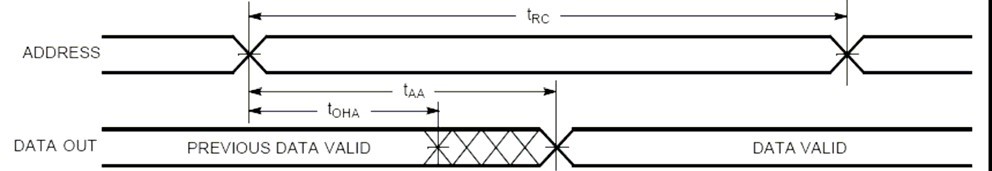

图5为CY7C1069AV33读时序,其中置CE1=VIL,CE2=VIH,WE=VIH.

图5, CY7C1069AV33读时序图

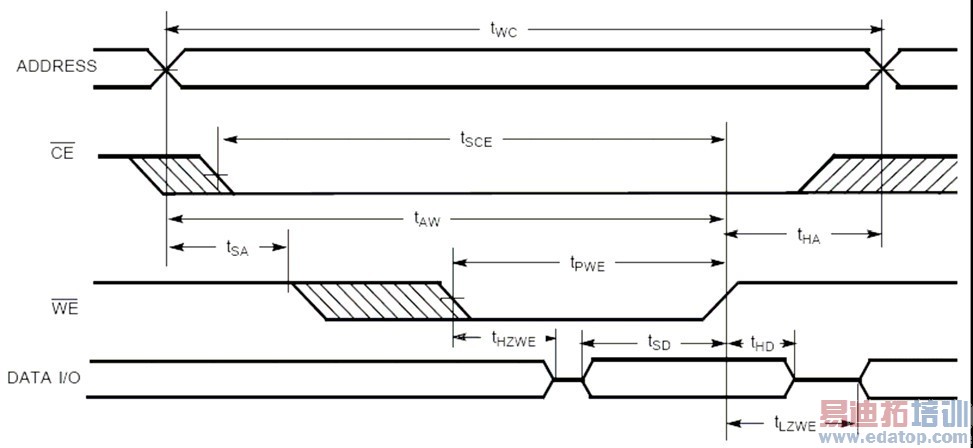

图6为写时序,其中置OE为低电平。

图6, CY7C1069AV33写时序图

3) 基于PSoC3 UDB 的SRAM模块设计。

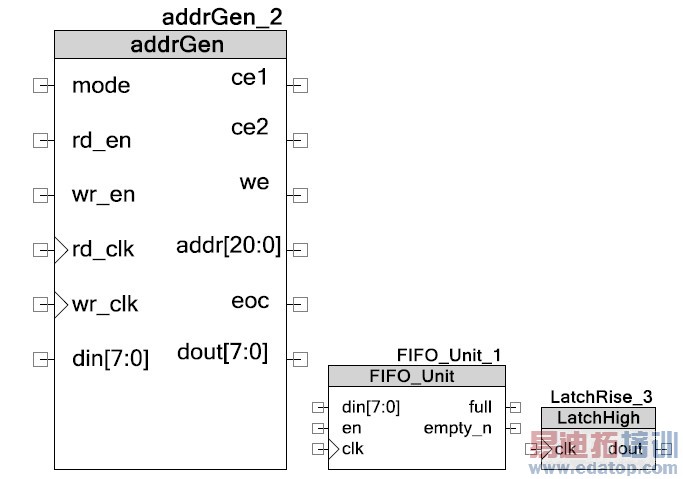

在SRAM读写过程中,一共使用了3个主要模块,这些模块是在PSoC Creator中生成的。addrGen模块是产生SRAM读写所需要的时序,包括地址线、数据线和控制信号线时序。FIFO_Unit模块是采用PSoC3 Datapath里的数据FIFO保存从SRAM里读过来的数据,作为临时缓冲。LatchRise模块类似DFF触发器,用于锁存信号的上升沿。

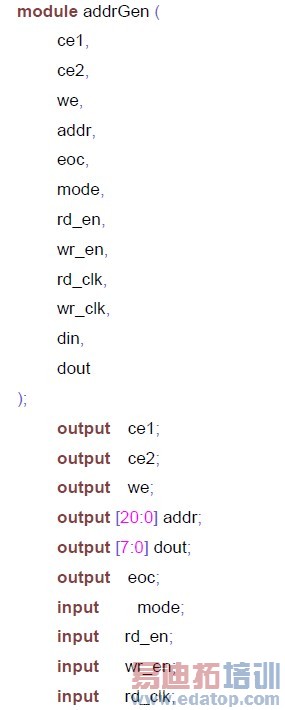

这里重点介绍一下addrGen模块在PSoC3 UDB中的Verilog设计。

模块接口定义:

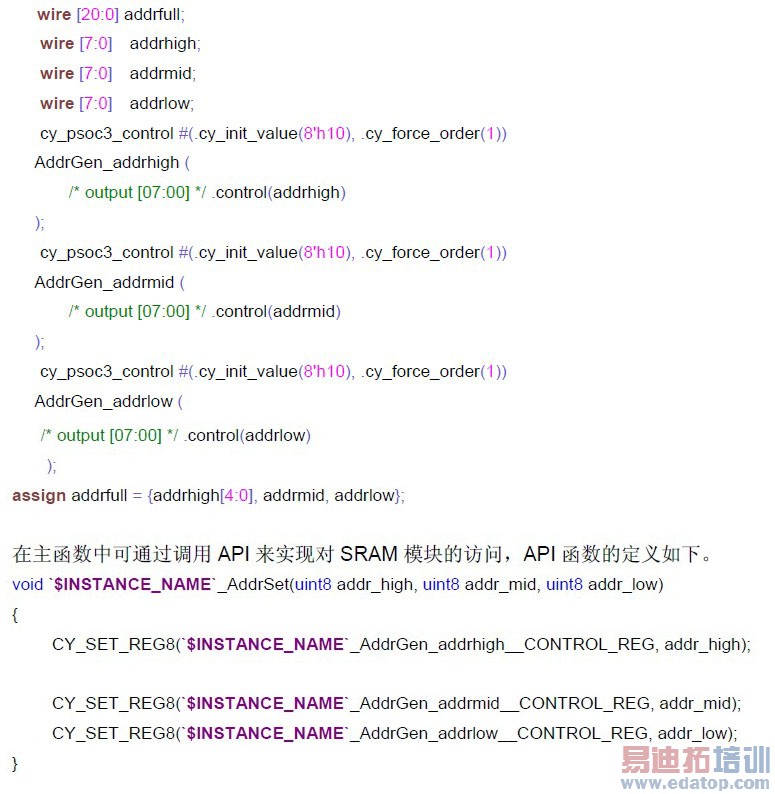

起始地址参数传递,在PSoC3中CPU可以通过控制寄存器来传递参数到UDB中。下面的示例代码为传递一个21bits的起始地址到UDB中。

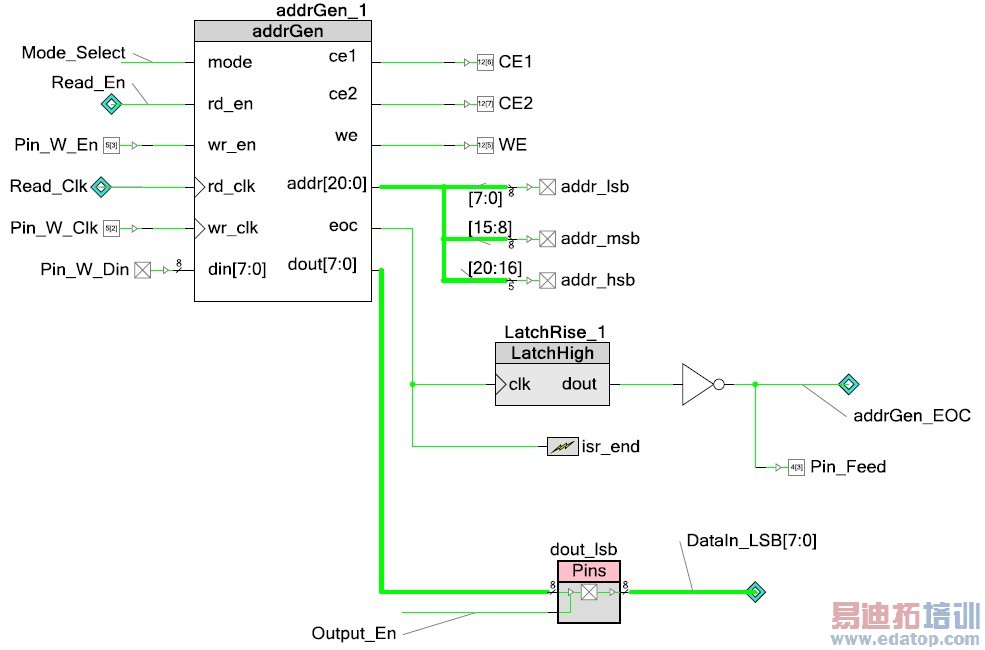

4) PSoC Creator中SRAM 读写原理图。

图7,读SRAM原理图

En_R_Reg是控制寄存器,用来启动SRAM读操作。地址、数据及控制信号由图8产生。当读完8bytes数据存放在Datapath的FIFO中后,FIFO_Unit模块会产生FIFO 满(full)信号,LatchRise将锁存该上升沿信号并置Read_En信号为低。这时CPU可将数据从UDB的FIFO中读出。然后再复位LatchRise模块继续读SRAM操作。

图8,SRAM地址数据产生原理图

Pin_W_Din为8位外部数据输入,当执行读操作时Read_En和Read_Clk有效,并置Mode_Select=1;当执行写操作时Pin_W_En和Pin_W_Clk有效,并置Mode_Select=0.

3 SRAM模块测试

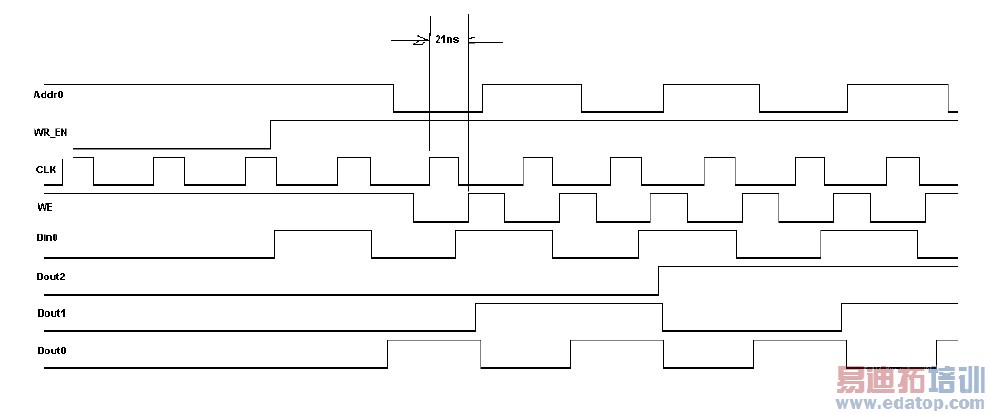

经测试,该模块工作正常,当数据从外部模块输入时其最高写SRAM速度可达20MHz,用逻辑分析仪测量SRAM模块的部分引脚信号如图9所示:

图9,SRAM模块部分引脚信号图

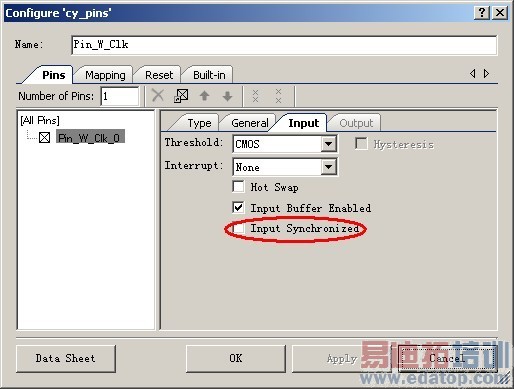

从上图可以看出,输入信号经过PSoC3 UDB后是有些延时的,大约21ns左右。这是在去除输入引脚的同步功能后得到的延时,输入引脚的同步配置如图10所示:

图10,输入引脚同步配置

若在输入引脚配置上选择"Input SynchrONized",则上面延时可能达到45ns,因此在设计时需要考虑到这些信号的延时。

来源:电子工程专辑