- 易迪拓培训,专注于微波、射频、天线设计工程师的培养

在40G/100G应用中使用10-Gbps收发器

作者:Altera公司

本文简介:主要了介绍向100G 接口过渡的关键推动力量,以及怎样利用FPGA 特有的功能来实现这一高速接口。数据中心以及核心网系统中新出现的40GbE 和100GbE 标准主要依靠FPGA 来链接本系统和其他协议的基础设备。Stratix IV 器件提供的资源是前所未有的,例如逻辑、片内存储器和DSP 模块等,是唯一支持需要10G 收发器数据速率40G/100G 设计的FPGA 系列,其优异的低抖动性能满足了高速设计的需求。

引言: 随着技术的进步,最新一代FPGA 提高了带宽,收发器数量越来越多,可以在单个器件中实现多种协议标准。FPGA 能够满足高速数据速率和带宽要求,新的目标市场定位在电信设备生产商上,这些生产商主要为40G 和100G 以太网(GbE) 开发新一代桥接应用和交换解决方案。

本文介绍向100G 接口过渡的关键推动力量,以及怎样利用FPGA 特有的功能来实现这一高速接口。该协议的标准化进展对于其实现非常重要,使其最终能够降低关键昂贵元件的成本,以高性价比方式实现量产。符合公共接口标准有助于简化体系结构和器件工作。以太网10/100/1000 Mbps 和10 Gbps 接口定义已经完善,目前的标准处于10 Gbps 以上接口的起草阶段。

数据中心以及核心网系统中新出现的40GbE 和100GbE 标准主要依靠FPGA 来链接本系统和其他协议的基础设备( 这包括光纤通道、Infiniband 和SONET 等桥接和数据汇集等应用)。LAN 速率提高到千兆位,性价比最好的网络采用以太网作为主要的数据链路协议,具体实现由ASSP 和FPGA 完成。但是,当LAN、SAN 和MAN 速率超过10G 之后,高性价比的网络采用了多种数据链路协议,必须使用多种ASSP,或者FPGA 作为桥接器件来提供高性价比解决方案。

满足40G/100G 需求

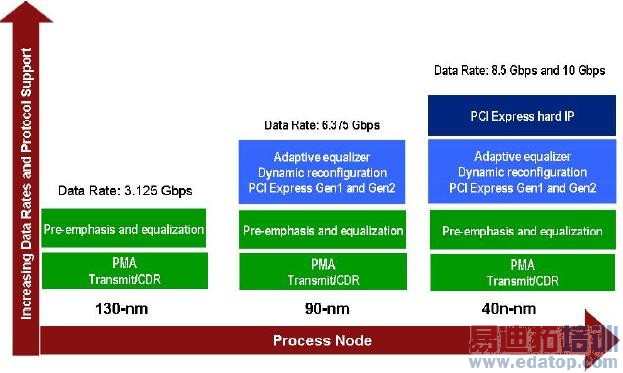

FPGA 经历了几个工艺代的发展,满足了40/100G 的需求,如图1 所示。在130-nm 工艺节点,FPGA 仅支持3.125 Gbps,而现在的40-nm 工艺节点能够支持10 Gbps 以上的数据速率。

图1. 工艺节点代

Altera StratixIV GX FPGA有32个嵌入式收发器,支持600 Mbps到8.5 Gbps的数据速率,另外16个收发器支持600 Mbps 到6.5 Gbps 的数据速率( 总共48 个速率达到6.5 Gbps 的收发器)。收发器包括物理编码子层(PCS) 和物理介质附加子层(PMA),这两个子层使Stratix IV FPGA 能够实现标准和专用协议。

图2 为Stratix IV GX 收发器模块结构图

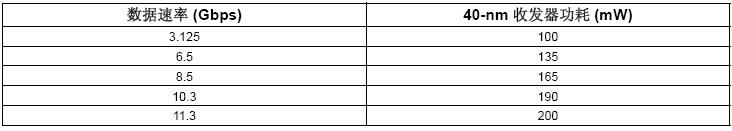

从一个工艺代发展到下一工艺代, FPGA 密度几乎加倍,过渡到更小的工艺尺寸能够大大提高芯片中的系统集成度。增强FPGA 的功能虽然很重要,但更重要的是以更低的功耗实现最前沿的系统性能。Stratix IVFPGA采用了成熟可靠的工艺以及可编程功耗技术和动态片内匹配等体系结构创新技术来降低40G和100G应用的系统功耗,同时支持较高的系统带宽。PMA 是一种嵌入式宏,专门用于接收和发送片外高速串行数据流。PMA 通道包括全双工通路( 发送和接收),带有I/O 缓冲、可编程输出电压、预加重和均衡、时钟数据恢复(CDR) 和串化器/ 解串器(SERDES) 等模块。表1 列出了Stratix IV GX FPGA 每个通道的收发器功耗。

表1. 每个通道的收发器功耗( 仅PMA)

表1. 每个通道的收发器功耗( 仅PMA)

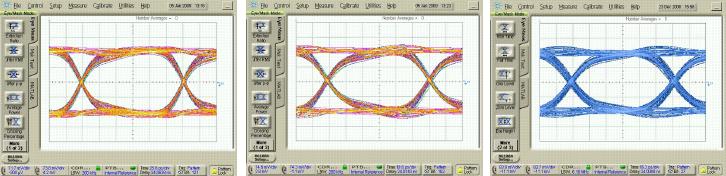

Stratix IV GX 收发器采用了先进的电源稳压和滤波技术,以降低发射器抖动,提高接收器抖动容限。因此,在实际系统链路中,收发器表现出优异的误码率(BER) 性能。发送和接收锁相环(PLL) 片内稳压器、敏感模拟电路的仔细隔离以及大量使用管芯和封装去耦合电容,都有助于为收发器提供可靠的电源分配方案,同时为模拟电路提供非常干净的电源。图3 显示了发射器在6.25 Gbps、8.5 Gbps 和10 Gbps 工作时的眼图。

图3 发射器在6.25 Gbps、8.5 Gbps 和10 Gbps 工作时的眼图

1 2