- 易迪拓培训,专注于微波、射频、天线设计工程师的培养

基于FPGA的PROFIBUS

图2所示是光电收发器的硬件结构框图。该设计方案整体上由DP总线数据收发部分、光纤数据收发部分和数据传输方向控制部分组成。 FPGA作为主控制器负责控制数据传输的方向、检测波特率和数据交换功能。其中电源部分采用隔离的DC/DC来减少外部电路的影响。电端DP总线的RS-485收发器可选用SN75HVD06D,该芯片可支持10 Mbps数据速率;而光端的数据接收器和发送器则可选择AVAGO公司的光发送器HFBR-14x4Z和光接收器HFBR-24x2Z,它们在50mA电流驱动下,其62.5/125μm的多模光纤传输距离可达2 km。FPGA芯片选用ALTERA公司的Cvclone系列芯片EPlC3T144C8N,该芯片有2910个LE单兀、1个PLL和144个IO引脚,且性价比较高。

3 FPGA逻辑设计

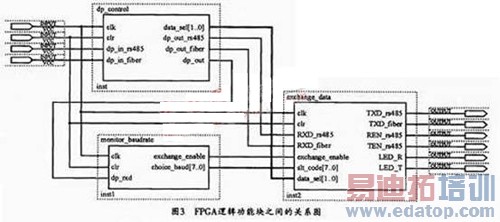

FPGA包括数据传输方向检测功能块、波特率检测功能块、数据交换功能块等三个逻辑功能块。它们的电端和光端都默认为接收状态。数据传输方向检测功能块用于判断哪个端口先来数据,然后把该端口数据输出到波特率检测功能块以检测其数据波特率,数据交换功能块可根据确定好的数据传输方向和波特率来切换RS-485收发器的收发状态,并最终实现数据的光电转换传输。该三个逻辑功能块之间的关系如图3所示。

3.1 数据传输方向检测逻辑

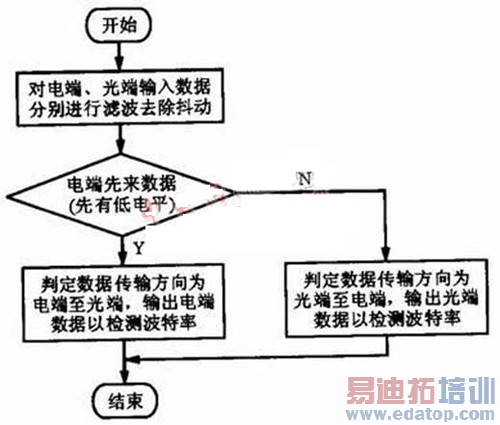

PROHBUS-DP总线协议的传输依赖RS-485接口,故在总线空闲状态下,依靠RS-485接口前端的上拉和下拉电阻即可保证总线上的电平为"1",RS-485收发器一般默认为接收状态。由于RS-485数据传输为半双工方式,同一时刻。线上的数据传输方向是单向的,且传输数据字节的起始位为低电平,这样,就可以根据电端接收数据和光端接收数据的低电平到来的先后顺序来判断数据的传输方向是从电端到光端,还是从光端到电端。为了避免由于线路上的干扰或者数据收发元器件的特性造成的毛刺,可对接收到的电端数据和光端数据先进行滤波去抖动处理。图4所示为数据传输方向检测流程图。