- 易迪拓培训,专注于微波、射频、天线设计工程师的培养

基于CPLD的RS

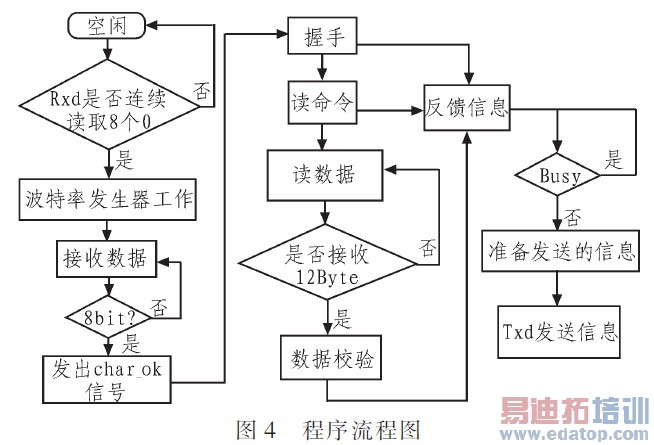

逻辑控制模块、数据接收模块和发送模块的设计都使用到了状态机,其中以逻辑状态机为主状态机,其余两个为从状态机。确定各种工作状态和工作流程后便可构建出状态图,方便直观地进行后续设计。

通过状态图可以方便、准确地得到程序设计框图如图4所示。

能得到较好的实验数据。

3 各模块设计

3.1 波特率发生器

串口通信必须要设定波特率,本设计采用的波特率为9 600 bit/s.产生波特率的时钟频率是越高越好,这样才可产生较高且精确的波特率。设计选用50M主频率要产生9600bit/s波特率,每传送一位数据需要5 208.33个时钟周期。取一个最接近的数是5 208,则波特率为9 600.61,其误差约为0.006%,误码率很低可以确保通信正常。

波特率发生器要解决的另一个关键性问题是确保准确地捕获起始位"0"。即时准确地捕获起始位不仅决定通信是否顺畅开始,而且还影响后续的数据采样过程可靠地进行。方案采取了16分频的波特率发生器,即通过对50 M总时钟源分频,得到一个9 600x16 Hz的时钟进行数据传输,这样每16个时钟信号采样1 bit数据。在Rxd数据接收端口接收到从空闲高电平"1"跳变为起始位低电平"0"信号后,连续8个分频周期确认是否是起始位。若是连续的低电平则捕获起始位,自此之后每16个时钟周期读取1 bit数据。这种方法不仅确保了起始位的准确捕获,而且使数据采样点处于了数据的正中央保证了数据的准确。

3.2 接收器

在波特率发生器捕获起始位并启动后,接收器将开始工作。其主要工作是接收每一位数据,将串行数据移位存入缓冲寄存器,并在接收完一字节数据后将数据存入锁存器完成串并转换,同时发出char_ok信号通知逻辑控制模块一个字节的数据已经接收完毕。

接收器的部分程序如下所示:

3.3 逻辑处理模块

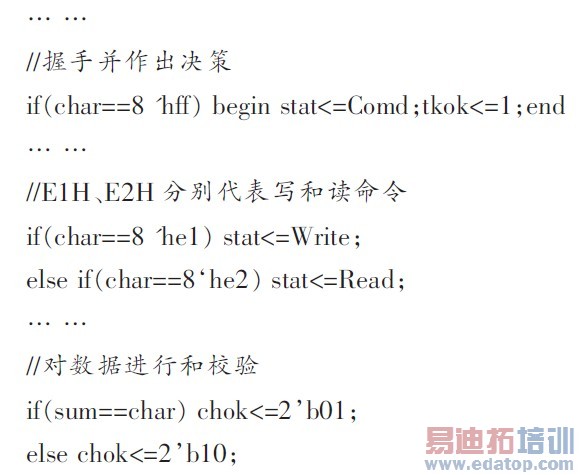

逻辑处理模块是模拟UART的决策模块。它主要完成PC机与CPLD的握手、数据处理和数据校验、状态分析与给收发模块提供决策。

PC机要向CPLD发数据时,先向串口发送FF,FF表示PC机要与CPLD建立联系。CPLD收到这个信息后,由逻辑模块的talk信号通知发射模块握手情况,发送器通过串口给PC机反馈信息,DD表示CPLD收到了PC机的要求并同意建立联系,CC表示握手不成功PC机可以再次发出请求。握手成功后,PC机要向CPLD发出命令字符,E1表示写,E2表示读。

随后进入数据接收或发送状态,每个数据包接收完毕后逻辑处理模块进入下一状态--数据校验状态。根据上文提到的本设计的数据校验采用和校验,数据校验完后逻辑处理模块会根据校验结果给出信号check,通知发送模块Txd发送反馈信息给PC机。

逻辑控制模块的部分程序如下所示:

上一篇:铜缆布线还能走多远?

下一篇:工业以太网技术相关问题浅析