- 易迪拓培训,专注于微波、射频、天线设计工程师的培养

FPGA的通信系统基带验证平台的设计

在Virtex-Ⅱ器件内部,所有DCM模块通过时钟多路复用器逻辑分配到器件内部。所提供的16个全局时钟缓冲器可实现16个时钟域的控制,保证了DCM模块的时钟输出具有最小的传输延迟(Skew)。

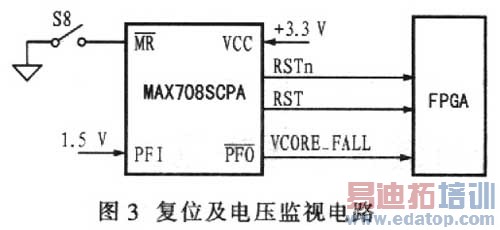

复位及电压监视电路采用MAX708SCPA,提供上电自动复位及手动复位。

MAX708SCPA的PFI引脚为监视电压输入端,当PFI输入电压低于1.25 V时,PFO引脚输出低电平表示电压过低,本设计中用于监视FPGA 1.5 V内核电压。

开关按钮S8提供手动复位。其电路示意图如图3所示。

3.3 数模和模数转换电路

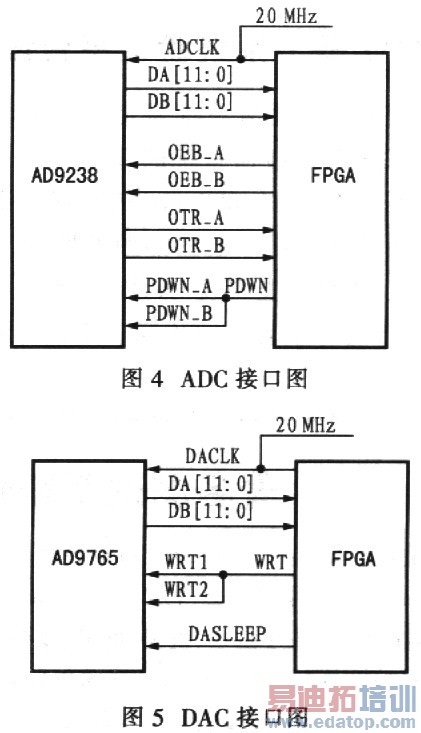

本平台用于验证通信基带系统,需要将发射机输出的I路、Q路信号通过数模转换器(DAC)转换成模拟信号,接收机则通过模数转换器(ADC)将接收信号转换成数字信号。本平台设计采用的ADC和DAC分别为ADI公司的AD9238和AD9765。

AD9238是双通道12位ADC。速度等级分为20MS/s、40MS/s和65MS/s。功耗为180mW~600mW,适用于要求低功耗和较小PCB面积的应用。AD9238的信噪比(SNR)为70 dB,无杂散信号动态范围(SFDR)为85 dBc。带有片内宽带差分采样保持放大器(SHA),允许用户选择多种输入范围和失调电压,包括单端输入。AD9765是双端口、高速率、双通道、12 bit的CMOS数模转换器(DAC)。它集成了2个高性能的12 bit TxDAC。更新速率可达125 MS/s,无杂散信号动态范围(SFDR)为75 dBc,O.1%的增益偏移匹配率。输出为差分电流、满幅度为20mA。

本设计中,AD9238工作在2Vp-p差分工作模式,采用内部参考电压,两通道工作在共享电压参考模式。输入差分幅度为2 V。信号时钟输入可以采用时钟驱动器的20MHz输出或由FPGA提供,最高采样率为40 MS/s。AD9238的两通道选择AD8138作为运放驱动器,为ADC提供差分输入信号。AD9765工作在双端口模式,两通道增益控制可分别调整,采用内部l.2 V参考电压。时钟输入也可以采用时钟驱动器的20 MHz输出或由FPGA提供。AD9238和AD9765与FPGA的连接示意图分别如图4和图5所示。

作者:沈梁 蒋一琦 来源:国外电子元器件

上一篇:微波通信新发展与通用发射机技术研究

下一篇:微波通信与应用