- 易迪拓培训,专注于微波、射频、天线设计工程师的培养

3G系统中AGC的FPGA设计实现

录入:edatop.com 点击:

3 AGC系统的FPGA实现

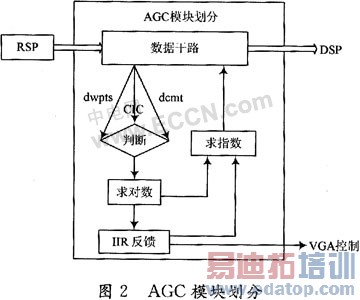

根据AGC所实现的功能,在FPGA中将AGC模块分为如下几个部分来实现:

3.1 数据千路模块

从RSP接口来10位二进制补码数据I1和Q1,与求指数模块传送来的预放大增益GAIN2相乘后所得出的数据(仍取10位二进制补码数据)将要传送到CIC平均模块,同时要分别与求指数模块传送来的放大增益GAIN3相乘,然后采取截短处理,取8位二进制补码数据,I1′,Q1′,输出到DSP中。

3.2 计算下行同步码功率(SYNC_DL)模块

计算下行同步码功率(SYNC_DL)模块对应于图2中的判断部分,是AGC中最为重要算法计算。TD_SCD-MA每个帧有6 400个码片,在其一帧5 ms的时间上是不连续的,因此只能求出下行同步码(SYNC_DL)的功率值,以此为依据控制VGA的电压值。

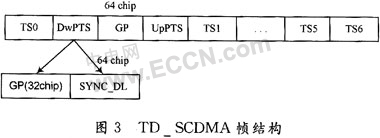

由图3的TD_SCDMA的帧结构知道,下行同步码(SYNC_DL)在下行导频时隙(DwPTS)发射,SYNC_DL的长为64个码片,在其左边和右边各有32和96个码片的保护时隙(GP)。为此,在FPGA中共用了3种不同的方法计算其功率值。

来源:现代电子技术