- 易迪拓培训,专注于微波、射频、天线设计工程师的培养

FPGA片上系统的无线保密通信终端

录入:edatop.com 点击:

数据可靠传输

为了确保数据不出错和不丢失,本设计采用了CRC校验、超时重传、返回ACK和NOACK等措施来确保数据的不出错和丢失,

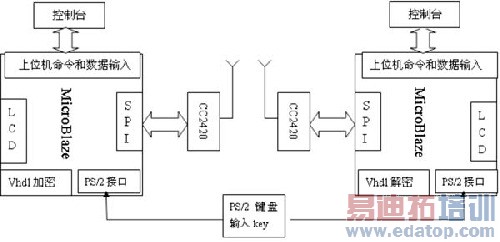

系统模块构成

加密端通过串口和网口从发送段接收数据,当接收够16字节(128bit),或不足时能自动补零成128bit后送给硬件AES加密模块。在软核Microblaze的控制下通过VHDL编程的AES加密后将数据进行组帧打包,通过软核对CC2420的寄存器的读写将数据通过无线发送端CC2420发送出去,同时等待发送段确认。接收端在接收到数据以后,从数据包中将数据提取,进行快速AES解密,解密完成后进行CRC校验,如果校验正确则向源地址发送ACK确认。将正确数据送出,如果校验失败,则返回NOACK。为了确保安全,AES加解密算法需要的密钥key由键盘输入和修改,同时可以在LCD上显示出来。必须保证两端key相同才能保证正常通信。

图1 系统总体控制数据流图

作者:毋杰 康丙寅 王昭婧 黄克军 电子科技大学 来源:电子产品世界

上一篇:802.11n无线网络技术剖析

下一篇:精细化无线覆盖方案应用