- 易迪拓培训,专注于微波、射频、天线设计工程师的培养

多路同步串口的FPGA传输实现

录入:edatop.com 点击:

FPGA处理模块实现

DSP的串口传输方式为同步串口,每组DSP串口有4个端口,分别为:clk , frame , data_a,data_b[3]。数据端口有两个,本例中只使能data_a,以下统一称为data。

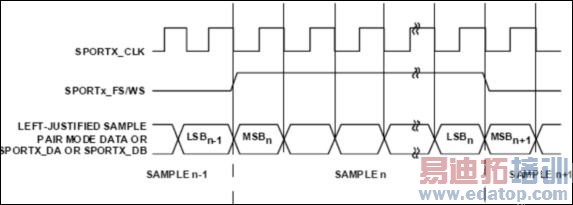

DSP同步串口传输时序如图2所示,当frame为1时,串行数据有效,当frame为0时,一帧数据传输结束。本例中DSP传输的一帧数据为32bit。

图2 DSP同步串口传输时序图

FPGA内部采用异步FIFO解决DSP时钟频率和FPGA时钟频率不匹配的问题,写时钟由DSP输出的同步时钟信号提供,时钟频率为60MHz;读时钟由FPGA的锁相环PLL时钟提供,PLL输出时钟频率为100MHz。

接收模块

由于DSP的8个同步串口同时写入,FPGA数据接收模块一共有8个,每个模块接收到的数据都存放在一个特定的FIFO中,将其称之为R_FIFO。

DSP输出信号为frame,clk, data,FPGA以DSP同步串口的输出时钟clk作为采集数据的时钟。系统上电结束后,FPGA等待ARM发送接收允许指令,接收允许后,FPGA就可以开始接收数据。

来源:电子产品世界