- 易迪拓培训,专注于微波、射频、天线设计工程师的培养

数字直放站中CPRI协议的FPGA实现

录入:edatop.com 点击:

2.2.1 CPRI链路层协议实现模块

CPRI链路层只是定义了一个同步的帧结构,而里面的IQ数据和控制管理数据都是由用户按需求自由处理的,采用FPGA实现CPRI的成帧、解帧及相关的控制,处理灵活,方便以后服务增加进行升级。在下面的软件部分做详细介绍。

2.2.2 CPRI物理层协议实现模块

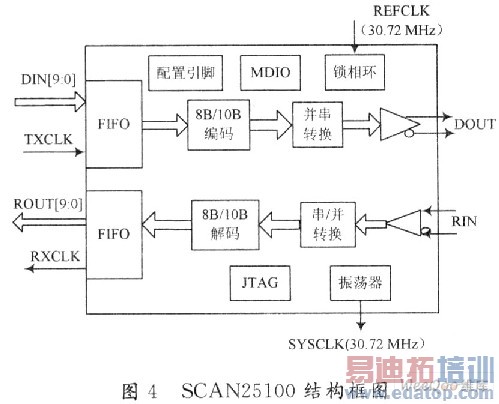

采用国半的CPRI串行/解串器SCAN25100。SCAN25100是专门为CPRI协议设计的高速串并转换芯片,除了串并转换之外,还有8 B/10 B编解码功能,其内部结构框图如图4所示。

图4中的TXCLK和RXCLK都是双边沿采集数据,降低了频率要求,光纤接口(DOUT和RIN)的速率由TXCLK决定,当TXLCK为61.44 MHz时,经8 B/10 B编码,再并串转换后,DOUT的速率就是1 228.8 Mb/s。对于RXCLK也就是接收过程的时钟,可以采用芯片内部自动恢复模式。当作为RE端时,内部振荡器产生的30.72 MHz时钟SYSCLK可以直接作为参考时钟REFCLK,省去一个精准的外部时钟,而且可以利用芯片上的两个锁相环路自动将远程射频单元同步到负责基带处理工作的基站。当作为REC端时,需要由时钟芯片产生30.72 MHz的时钟给SCAN25100当参考时钟。具体应用时,可以使用芯片的配置引脚进行芯片工作模式配置,也可以用MDIO接口对芯片内部寄存器进行编程,达到配置芯片的目的。

来源:维库开发网