- 易迪拓培训,专注于微波、射频、天线设计工程师的培养

Virtex-5 FPGA设计Gbps无线通信基站设计

录入:edatop.com 点击:

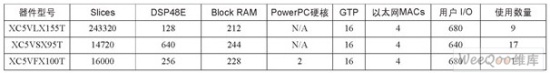

其中,发送端的LDPC编码和接收端的LDPC译码,主要是逻辑运算,无需乘法器资源,因此采用Virtex-5中的LXT实现。同步、FFT/IFFT、调制/解调、空时译码等算法需要消耗大量的乘法器资源,采用集成大量DSP48E模块的SXT系列实现。MAC处理及网络接口采用FXT系列FPGA中的2个PowerPC440处理器以及内嵌的千兆以太网硬核实现。采用FPGA片内的PowerPC处理器,可以大大地降低外部电路设计的复杂度,降低物理层与MAC层间数据交换的复杂性,降低系统传输延迟,而且可以利用PowerPC处理器应用处理加速单元(APU)实现定制的指令,极大地提高MAC处理的效率。

表 2 基站中使用的Virtex-5 FPGA资源及数量统计

基于Virtex-5 FPGA设计的Gbps无线通信基站

图2是设计完成的Gbps无线通信基站基带处理系统硬件实现框图。

图 2 Gbps无线通信基站基带处理系统硬件实现框图

来源:维库开发网