- 易迪拓培训,专注于微波、射频、天线设计工程师的培养

三线制同步串行通信控制器接口设计

录入:edatop.com 点击:

时钟分频模块主要用于数据收/发模块产生同步时钟信号。

系统接口控制逻辑主要用于各种逻辑功能信号的控制,同时还可以接收_中断仲裁逻辑模块产生的中断信号,控制数据的接收或者发送操作。

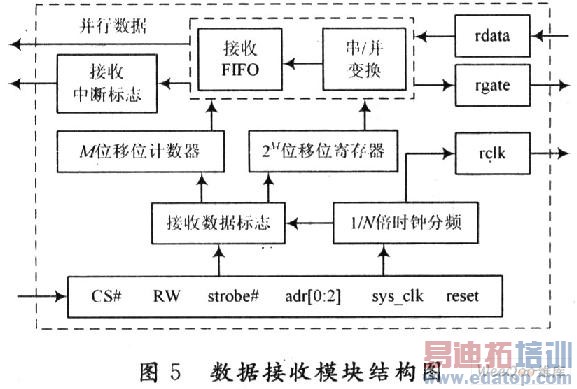

数据接收模块是三线制同步串行通信控制器接口进行数据接收的核心部分,其模块结构如图5所示。

数据接收流程:在帧同步脉冲信号触发下,串行数据在时钟信号rclk上升沿到来时保持稳定,并通过rdata信号线进入数据接收模块。

在该模块内部,串行数据经过串/并变换,接收FIFO作为数据缓冲器,将接收到的数据锁存在VHDL程序指定的两个地址寄存器中,一个地址单元存储数据的高八位,另外一个地址单元存储数据的低八位,当数据存满这两个地址单元后,接口向系统发出一个"接收缓存满"的接收中断标志int,系统微处理器响应后,数据被全部取出,并行数据被送往系统的数据总线上,重复进行相同操作,直至连续接收完所有数据,数据接收过程结束。

来源:维库开发网

上一篇:无线信道

像传输系统设计

下一篇:基于DSP的调幅广播信号监测系统