- 易迪拓培训,专注于微波、射频、天线设计工程师的培养

三线制同步串行通信控制器接口设计

录入:edatop.com 点击:

从图2中可看到,通过复位信号rstn、片选信号CS、门控信号strobe和读写信号RW等的不同组合,实现逻辑控制功能。通过异步四位计数器SN54HC161的计数功能,使得移位寄存器SN54HC164顺利进行数据的串/并转换,将8位并行数据通过8位D触发器SN54HC374锁存在内部总线上等待系统接收。在输出端,通过双D触发器SN54HC74产生中断信号int,通知系统内的微处理器进行数据接收操作。

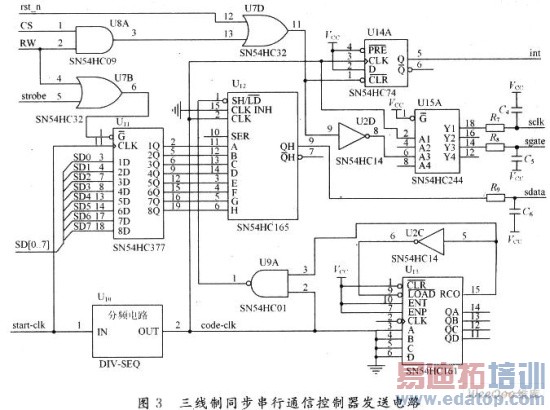

三线制同步串行通信控制器发送接口硬件电路如图3所示。

从图3可知,系统时钟start-clk通过分频电路模块产生发送时钟原始信号code-clk,用于电路的时钟状态控制。系统内的微处理器将要发送的8位并行数据通过8位D触发器SN54HC377,将数据锁存在其Q端口等待发送,然后在异步四位计数器SN54HC161的计数功能控制下,移位寄存器SN54HC165进行数据的并/串转换操作。在输出端,通过双D触发器SN54HC74产生中断信号,然后开始通过单向总线驱动器SN54HC244进行帧同步信号、时钟信号及数据的发送操作。

来源:维库开发网

上一篇:无线信道

像传输系统设计

下一篇:基于DSP的调幅广播信号监测系统