- 易迪拓培训,专注于微波、射频、天线设计工程师的培养

TD-SCDMA射频前置分频器的设计

在射频CMOS电路中,锁相环(PLL)是重要的组成模块之一,主要是通过频率合成,产生本振信号。用于TD-SCDMA的PLL模块需要更宽的频率范围和多种频率本振信号。因此更需要在通过小数分频等多种方式实现低功耗情况下,更快的锁频功能。双模分频器(Prescaler)工作在电路较高频率,功耗也较大,研究和开发双模分频器对于降低整片功耗,提升PLL性能有着重要意义。

1 TD-SCDMA标准特点及关键技术

TD-SCDMA技术灵活地综合了FDMA、TDMA和CDMA等基本多址接入技术。由于该标准的提出比其他标准晚,所以吸纳了移动通信领域最先进的技术,技术兼容性强,后发优势明显。

其主要特点包括:频谱利用率较高;支持多载频技术;呼吸效应不明显;组网灵活、频谱资源丰富;易与GSM网络兼容;灵活提供数据业务。

在无线接口技术上主要包括以下关键技术:动态信道分配;智能天线技术;接力切换技术和联合检测技术。

将我国3G公众移动通信系统主要工作频段规划为时分双工(TDD)方式,即1880~1920MHz、2010~2025MHz;补充工作频率为时分双工(TDD)方式,2300~2400MHz。

因为3G公众移动通信系统中TDD方式仅有我国的TD—SCDMA,根据上述规定,产业界为方便表达,称1880~1920MHz为A频段,2010~2025MHz为B频段,2300~2400MHz为C频段。目前主要频段选取B频段,A频段将在小灵通全面退市后逐步采用。

2 TD—SCDMA收发信机结构

TD—SCDMA系统频率范围为2010~2025MHz,带宽为20MHz。在一般的收发信机中,信道之间的干扰可以通过高质量的射频滤波器抑制,同时TD—SCDMA与其他两个制式的干扰需要在设计中考虑。

TD-SCDMA系统采用如图1所示的零中频结构接收机。射频接收信号经过滤波器、低噪放,与两路正交本振信号混频,产生同相、正交两路基带信号。由于没有中频,本振信号与射频接收信号频率一致,混频后直接产生基带信号,在基带信号中通过低通滤波器和放大器进行信道选择和信号放大。

零中频结构的优点在于不需要中频而变得简单,由于本振信号频率与射频接收信号相同,不存在镜像干扰,不需要片外高Q值带通滤波器,也使集成度更高,更适合TD设计需要。同时电路简化和外部器件删除也使功耗降低,干扰和故障点变少。缺点在于直流偏差、本振泄漏、偶次失真、闪烁噪声、I/Q失配等问题,使用零中频结构首先要解决好这些问题。但是总的来说,零中频结构简化了电路,更适于片上设计,具有一定优势。

发射机与接收机结构相反,也采用零中频方式,在此不再赘述。

3 锁相环频率综合器结构介绍

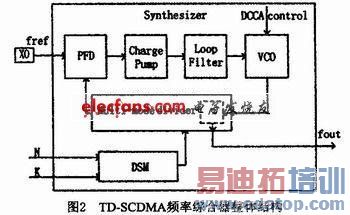

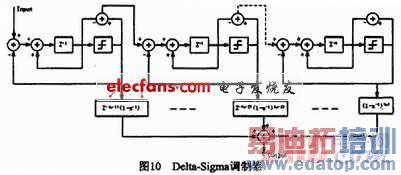

TD-SCDMA系统通过PLL式频率综合器产生本振信号。由图可见,该频率综合器主要包括鉴相器、电荷泵、低通滤波器、VCO,在反馈回路上包括多模分频器和Delta-Sigma调制器。其中多模分频器和Delta-Sigma调制器是我们的设计重点。

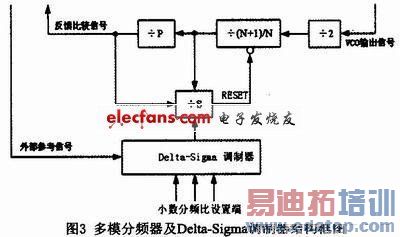

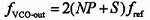

如图3所示,首先VCO输出信号进入一个固定二分频电路,这个固定二分频电路也是工作频率最高、功率最大的模块,它的设计将采用CML结构下,基于注入锁定振荡原理完成,尽可能实现低功耗和低噪声。之后是一个模8/9的分频器,其中采用相位转换结构减少功率损耗,提升转换速度。P分频模块为一个11分频固定分频器。S分频由Delta-Sigma调制器控制,实现小数分频。根据结构框图可以计算出输出频率fVCO -out与输入频率,fref的关系为:

由于输出频率范围为2010~2025MHz,参考频率10.8MHz,所以可以得出s分频范围在5.056~5.750。

4 电路级设计

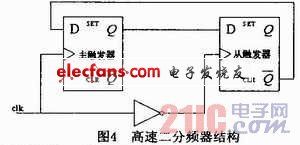

4.1 高速二分频器。

如图4所示,由于分频器工作频段在2010~2025MHz,所以高速固定二分频器工作频率在2GHz左右,通过分频,频率降低一半。实现形式,基于注入锁定理论,结构采用主从D触发器结构,通过负反馈结构形成环路振荡结构。

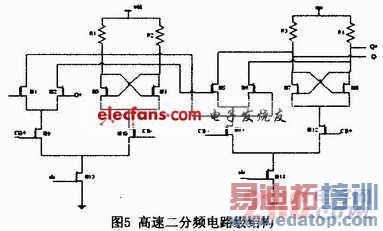

电路级结构,如图5所示。

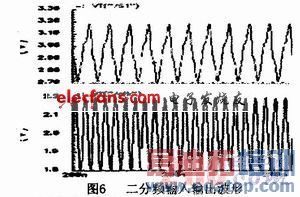

由图5可见,主锁存器承担了混频器功能,包括M9、M1和M2,其中M1M2为本振口,M9为参考信号口。实际设计中通过电路参数调整,将电路自由振荡频率w0=clk/2。通过尾电流及电阻调节w0。基于注入锁定的固定二分频器输入输出波形如图6所示。

4.2 相位转换模块

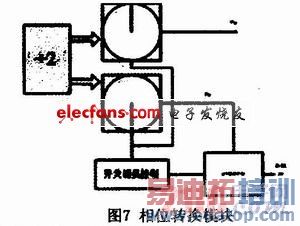

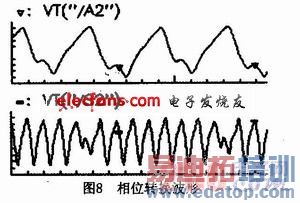

如图7所示,相位转换控制模块不再采用电平控制模式,采用Pn+1信号控制相位开关模块,即通过使用在切换目标信号的上升沿触发切换,避免了毛刺现象。

正常的分频为4分频,当K=1时,分频数为4+K,即为5分频。

4.3 异步分频链

异步分频由两个除2的分频器组成,每个二分频器为主从D触发器,电路采用CMI结构。电路为串接而成,工作频率相对较低。

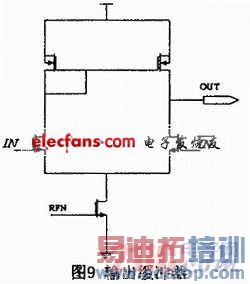

4.4 输出Buffer

输出Buffer主要起到放大成方波和整形作用,保证输出信号能够当作完整的本振信号使用。

4.5 小数分频模块

根据对小数分频器Delta-Sigma调制器结构的分析,综合考虑系统稳定性、噪声调制效果、带外噪声平滑、频率分辨率及设计难度和电路面积,主要为了保证稳定,选用MASH型结构Delta-Sigma调制器。

控制小数分频,实际分频比均值4.4375。

5 总结

前置分频器是PLL中重要的部分。本文在研究和分析国内外3G系统结构基础上,选定零中频结构收发信机中本振PLL反馈回路上分频模块作为研究对象,实现射频模式下准确小数级分频。

上一篇:高通创锐讯推出高整合度Wi-Fi连线解决方案

下一篇:无线激光通信光发射模块的设计