- 易迪拓培训,专注于微波、射频、天线设计工程师的培养

技术分析:动态功耗调节详解

在今天的数据采集系统(DAQ)中,需要不断突破性能极限。系统设计人员需要更高的速度、更低的噪声和更优的总谐波失真(THD)性能,所有这些都有可能实现,但却并非免费。实现这些性能改进通常需要更大的工作电流,而更大的工作电流则会产生更高的功耗。但是,在许多应用中,功耗敏感性也越来越受关注。原因有很多种。可能是由于应用是一种利用纽扣电池进行工作的远程系统,其主要关注点是电池寿命。也可能是由于应用是一种多通道系统,其通道数较多、电路密度较高,会造成热量集中,从而产生由温度引起的漂移问题。无论何种情况,最大限度降低电流消耗和功耗都是重中之重。系统设计人员必须权衡更高性能和更低功耗带来的竞争优势。解决此问题的一种途径是借助一个称为动态功耗调节(DPS)的过程。

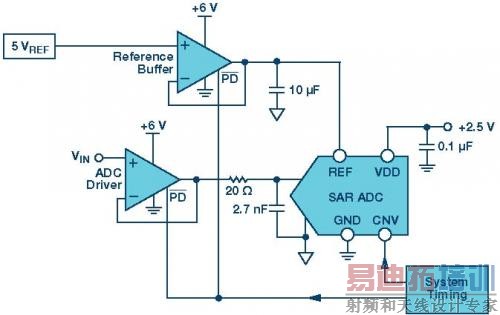

图1.基于SAR型ADC的数据采集子系统的框图

简单而言,DPS就是一个在需要时启用电子元件、在不需要时禁用电子元件的动态过程。图1所示为一个典型的基于SAR型ADC的数据采集子系统。SAR型ADC的一个主要属性是其功耗随吞吐速率而变化,这使其非常适合功耗敏感型应用。以往,ADC驱动器和基准电压源缓冲器不能与SAR一样享有自动功耗调节功能。它们通常会在系统运行时上电并启用,这样会消耗过多的电能。假设启用时间足够短,便可以动态方式驱动放大器关断引脚,从而禁用ADC转换之间的放大器。这就是动态功耗调节。通过对放大器运用DPS,可大幅降低其平均电流消耗。借助DPS,放大器静态电流随关断引脚正在被驱动的负载周期而变化。理论平均静态电流可由下式得出

其中:

本文的其余部分将聚焦于ADC驱动器放大器,但DPS概念也可运用至基准电压源缓冲器,而且得到的结果类似。

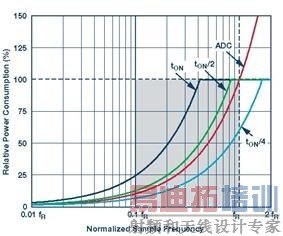

图2.在选定tON(与一直启用的放大器相关)时进行DPS的理论放大器功耗

动态功耗调节介绍

图2显示了ADC驱动器放大器在一直启用时的理论效率提升。fR处的竖直基准线代表ADC功耗等于一直启用的驱动器放大器的功耗时的采样频率。采样速率较低时,放大器的功耗占主导,采样速率较高时,ADC的功耗占主导。基准频率(fR)将随放大器和选定ADC的功耗而变化,但基本概念依然相同。进行功耗调节的同一放大器的相对效率提升以三种不同的tON值显示。不出所料,采样速率给定时,更小的tON会产生更高的效率,并且能够以更高的采样速率运用DPS。阴影区域表明,逐渐减小tON产生的最大提升区域一般会延伸至约10个fR以下。由于采样速率会继续降至此点以下,因此可实现最大的整体功耗节约,但进一步减小tON带来的优势可以忽略不计,因为功耗逐渐接近关断或禁用状态的功耗。

要利用DPS获得最高的性能,系统时序和确定最小tON至关重要。

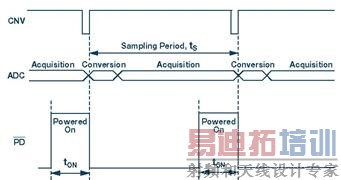

图3.放大器和ADC控制信号的简化时序图

图3所示为ADC和驱动器放大器的简化时序图。图1中的系统时序功能块(FPGA、DSP和微控制器)可提供恰当的定时ADC转换开始(CNV)和放大器关断(PD)信号。SAR型ADC会在CNV的上升沿启动转换。在CNV的上升沿前,放大器在ADC采集阶段上电一段时间(tON),然后与CNV的上升沿同步关断。tON的值为多大才恰当?

虽然图2说明了使用随机的tON值时的概念,但其清楚表明,DPS的全部价值将仅在使用最小tON时实现。这是放大器必须在ADC转换开始前启用以确保结果准确的最短时间。更短的时间将导致SNR或THD降低,更长的时间将不会引起任何性能提升。实际上最小tON在整个采样速率范围内并非固定,并且必须根据具体应用,用经验进行确定。最小tON因不同的放大器和系统而异。例如,如果在图1的电路中使用ADA4805-1和AD7980的放大器/ADC组合,则最小tON会随着采样速率的增大而减小。通常,1 kSPS时需要~4 μs,而1 MSPS时则只需要~600 ns。采样速率较低时,由于处于关断状态的时间延长,因而较长的一段时间会为内部放大器节点放电提供更多的时间,因而开启时间更长。相反地,采样速率更高时,此时间段更短,因而内部放电时间更短。事实上,随着采样速率提高,有限的放大器关断时间将变得长于在关断状态消耗的时间。实际上,放大器在完成关断过程前就已经重新开启。这看起来是人为式的快速开启时间,但在性能数据未减小时却十分有效。

预测潜在功耗节省量时需要考虑的最后一点是输入信号频率的影响。迄今为止,我们已通过使用给定放大器的计算静态电流对DPS的概念进行说明。将一个信号施加在放大器输入时,也会出现随输入信号频率增大而增大的动态电流。如果输入频率足够低,影响微乎其微。随着频率增大,放大器输出端的RC网络会显示更大的负载,因而需要放大器提供更大的电流来处理此信号。

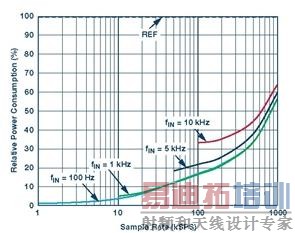

使用前面提及的ADA4805-1和AD7980并将这些概念综合在一起便可得到图4中的曲线。此图显示了进行动态功耗调节的ADC驱动器放大器相对于同样的放大器在一直启用时的功耗(用百分比表示)。我们绘制了选定输入频率下的DPS效率图,用以描述更高的输入频率对功耗的影响。我们确定了介于1 kSPS至1 MSPS之间的多个采样速率的最小tON,并将其定义为导致SINAD(信噪失真比)与一直启用的放大器相比减小不超过0.5 dB的tON。此图显示,在低采样速率下处理缓慢输入信号时,功耗节省量最高可达95%。但对更高吞吐量的系统而言更重要的是,潜在功耗节省量仍然非常高,在100 kSPS时最高可达65%,在1 MSPS时最高可达35%。必须注意,图4反映的是一个单位增益缓冲器在持续被采样的系统中的性能。但是,如之前所述,可将这些DPS概念轻松运用至基准电压源缓冲器,而且得到的结果类似。

图4.放大器功耗与动态功耗调节的关系—试验结果

虽然DPS是一种相对较新的概念,而且需要考虑设计和时序因素,但是其初步成果非常有效。很明显,对更高性能和更低功耗的渴望将延续到未来,从而进一步增加对创意低功耗解决方案的需求。

作者简介

Bruce Petipas是ADI公司线性产品和技术部门的一位应用工程师。他从马萨诸塞大学获得电气工程学士学位后,于1999年加入ADI公司。在此期间,Bruce专攻高电流放大器的各个领域,最近,他开始致力于ADC驱动应用。

在线支持社区

访问ADI在线支持社区,与ADI技术专家互动。提出您的棘手设计问题、浏览常见问题解答,或参与讨论。

ez.analog.com

上一篇:工业物联网的发展之源

下一篇:三星Pay实测,支付体验上靠啥战胜微信支付宝