- 易迪拓培训,专注于微波、射频、天线设计工程师的培养

LMK0480X holdover 功能分析

3、Holdover 功能的参数设置

3.1 Holdover 功能的配置

使用holdover 功能,必须首先Holdover_Mode = Enable;在绝大多数的应用场景,内部的DAC 输出需要跟踪 VCXO Vtune 电压,所以EN_Track = 1; 并且跟踪电路的正常工作需要在PLL1 锁定之前设置EN_Track =1;否则,当PLL1 锁定之后,设置EN_Track=1 并不能使DAC 输出跟踪Vtune 电压。

DAC 的电压也可以是手动设置,此时需要EN_MAN_DAC = 1;同时LMK0480X 提供了两个寄存器,DAC_Low_Trip 和DAC_High_Trip, 用于设置DAC 输出电压的上下门限。

触发芯片进入holdover 状态,可以是以下任一条件:

Force_holdover = 1;PLL1 失锁 或DLD =0;

Vtune 或DAC 跟踪电压超出DAC_Low_Trip 和DAC_High_Trip;

在使用的过程中,需要根据不同的系统需求选择合适的holdover 触发条件;从目前来看,大部分应用场景选择PLL1 失锁或DLD = 0 触发holdvoer 状态。

最后还需要配置Holdover_DLD_CNT 以及DAC_CLK_DIV,这两个寄存器的功能在第二章中已经介绍。

3.2 Holdover 参数配置的注意事项

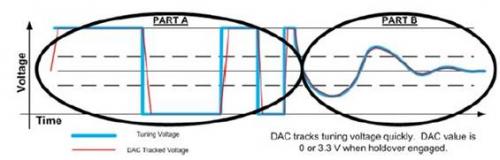

当系统上电开始工作是, CLKin0 或CLKin1 来自光纤的恢复时钟, 性能并不稳定。若Holdover_DLD_CNT 和PLL1_DLD_CNT 值设置比较小,LMK0480X 很容易进入锁定状态,本地时钟VCXO锁定CLKin 输入信号,同时DAC 开始跟踪VCXO 的Vtune 电压;但前面提到,通常CLKin 在刚开始工作时并不稳定,某些情况下CLKin 的输入可能漂出VCXO 的频率调整范围,导致器件重新失锁并进入holdover 状态,并且此时holdover 输出电压可能为3.3V 或0V;在这之后,CLKin 的频率渐趋稳定,但CLKin 的频率和VCXO(Vtune = 0V 或 3.3V)的频率不能满足退出holdover 的条件,出现了LMK0480X 无法退出holdover 的情况。如下图PartA 部分所示。因此,在holdover 功能电路设计中,通常适当的增加PLL1_DLD_CNT 和HOLDOVER_DLD_CNT 的值,使得退出和锁定的判决条件更为苛刻,只有当CLKin 稳定时,才会退出holdover,进入锁定。如下图PartB 部分所示。

另一方面,在第二章中分析得到,当PLL1_DLD_CNT 和HOLDOVER_DLD_CNT 的值过大时,会影响时钟切换的整个时长,所以在应用中,PLL1_DLD_CNT 和HOLDOVER_DLD_CNT 值得选取,是一个折中的过程;同时也可以通过芯片的配置流程对这个问题加以改善。

Figure 3 上电时参考时钟和holdover 关系

4、Holdover 功能在无线RRU 中应用的需求分析

4.1 C-RAN 网络架构的优势

随着电信业务的蓬勃发展与用户行为的不断变化,无线接入网正面临着前所未有的挑战:大量站点导致高能耗,网络的资本支出与运维成本逐年增高;站点资源难以获取;复杂的网络环境致使无线覆盖质量不高,潮汐效应导致部分基站利用率低下……面对技术、成本、资源和安全等多个问题 ,2010 年4 月,中国移动提出新一代绿色无线接入网架构C-RAN。

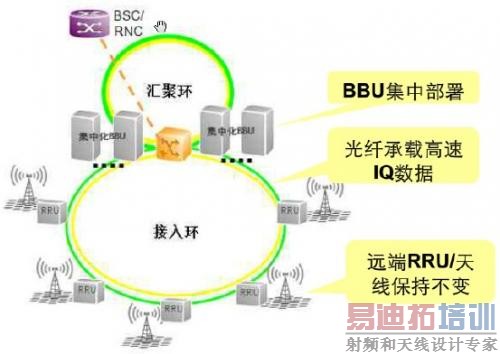

Figure 4 RAN 网络架构

C-RAN 架构是在分布式基站基础上的进一步创新,通过基带集中处理(Centralized)、协作式无线电技术(Collaborative)以及实时云架构(Cloud),实现网络资源共享以及动态的网络负载均衡,实现无线接入网的绿色高效(Clean)并面向未来平滑演进,提供更大的带宽和更灵活的多标准运营支持,如图4 所示。

4.2 C-RAN 网络中环形倒换对时钟指标的要求

在C-RAN 组网中,如图5,基带集中RRU 拉远需要光纤互联,采用多级级联和环形组网,一方面各站点RRU 通过光纤接入环采用环形组网方式接入BBU,有效节省光纤资源,另一方面这种组网结构支持环网倒换保护功能,充分保证网络安全和可靠性,即当任何一段光纤意外损坏或者链路中任一个RRU损坏, 会自动倒换到反向链路, 从而不会影响上级或下级RRU 的正常工作。

Figure 5 C-RAN 环形布网

RRU 级联系统在正常工作中,每个RRU 的系统参考时钟来自上一级RRU;当RRU 在完成环网倒换过程中, RRU 的系统参考时钟的来源也会切换,从切换前的来自上一级RRU 切换到另一侧的RRU;在整个切换的过程中,系统时钟必须保持一定的稳定度和准确度,从而保证现有用户不掉话,保证通话MOS和数据业务吞吐率。

以TD-LTE 系统为例,基站具体的时钟需求如下:

不同基站间空口同步信号相对时间误差小于+/-1.5us;

基站空口载波频率稳定度优于+/-0.05ppm;

基站输入抖动容限不小于±200ns;

BBU+多级RRU 串连级联时空口相对传输输出接口的时间精度小于±300ns;

在时钟切换的过程中,需要确保数字部分的FIFO 不要溢出,同时也要考虑频率误差带来的空口同步误差,小于系统的要求+/-300ns。

假定在切换过程中,频率误差为X*10e6 ppm, 每帧长度为Tf,则造成300ns 的空口误差需要的时间Ts 为:

Equation 6

Equation 6

假定X =  6, Tf = 0.01 S, 则Ts = 0.3 S, 即整个切换过程必须在0.3 S 内完成,否则频率误差可能造成空口的同步误差,造成TD 系统的收发切换紊乱。同理,假设FIFO 的工作时钟是Fclk,当FIFO 深度为1 时,造成一个码片误差的时间Te 为:

6, Tf = 0.01 S, 则Ts = 0.3 S, 即整个切换过程必须在0.3 S 内完成,否则频率误差可能造成空口的同步误差,造成TD 系统的收发切换紊乱。同理,假设FIFO 的工作时钟是Fclk,当FIFO 深度为1 时,造成一个码片误差的时间Te 为:

Equation 7

Equation 7

当FIFO = 491.52MHz 时,Te = 2mS. 可以看到这个要求是相当苛刻的;但这个问题可以通过增加FIFO 的深度来解决。当FIFO 深度为1000 时,Te = 2 S;但继续增加FIFO 深度已经没有意义,因为瓶颈已经变成了Ts。

通过同时可以看到,当提高切换过程中的频率稳定度,降低频率误差,可以延长切换过程需要的时间;反之,如果切换过程中频率度很差,则必须快速完成切换,否则很容易造成客户断链掉话。

根据第二章中介绍的LMK048XX 系列的介绍的holdover 功能,假定PLL1_WND_SIZE = 40nS, FPD1 =1.024MHz, Holdover_DLD_CNT = 4096,PLL1_DLD_CNT = 4096,DAC_CLK_DIV = 32,在整个切换过程中,总共用时为0.053(Texit _ holdover ) + 0.024(Tlock ) +0.016(Ttrack ) = 0.093s, 在切换过程中输出时钟的精度保持在0.5ppm。根据前面讨论的C-RAN 系统需求(切换时间<0.3s,频率精度<1ppm),LMK048XX 完全可以满足环形网络系统在倒换情况下的时钟精度需求。

5、总结

本文主要介绍了LMK048XX 系列时钟的holdover 功能。通过对C-RAN 系统时钟切换需求的举例分析,证明LMK0480XX 的holdover 功能真正的实现了hitless switch,完全可以满足通信系统的时钟切换功能,大大简化了通信系统的时钟单元的设计难度和成本。

6、参考资料

1. LMK04800 Datasheet

上一篇:博通公司推出世界首个28nm多核通信处理器系列

下一篇:Lantiq

全新VDSL芯片

为用户端设备(CPE)

树立性能标杆