- 易迪拓培训,专注于微波、射频、天线设计工程师的培养

使用Xpeedic SnpExpert 分析25Gbps高速背板连接器

摘要:背板是电信传输设备基础。在超大容量的骨干网传输设备中,25Gbps背板互连设计越来越普遍,通过背板传输的25G高速信号会表现出严重的信号完整性问题。本文以100GBase-KR4设计规范为基础,介绍25G高速背板设计中影响性能的主要因素,着重介绍高速连接器在背板设计中重要地位,并通过芯禾科技的仿真软件(SnpExpert)来评估高速背板连接器的各种参数及性能,指导SI工程师对连接器的正确选型及使用。

关键字:高速连接器,信号完整性,插损,回损

1.引言

当前的数据通信系统和计算机系统都依赖于高速串行数据传输。随着25Gbps以上串行链路应用的普及,信号完整性(SI)问题越来越突出。使用合适的设计工具和设计方法来分析传输通道中的各个环节,就可清楚地观察到这些复杂SI现象[1,2]:反射损耗,插入损耗,串扰,阻抗失配等。而连接器是高速传输通道中的重要组成部分,本文通过分析高速背板连接器的功能及特点,利用"SnpExpert" S参数分析软件对连接器参数进行分析。

2. 背板介绍及性能要求

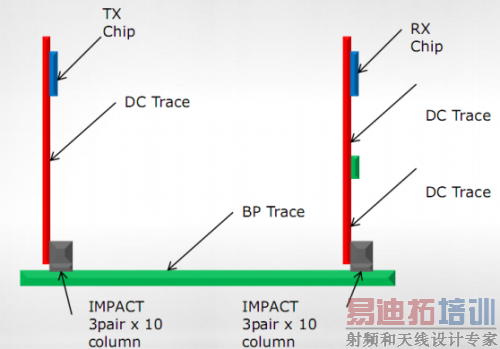

背板由许多不同组件组成,10Gbps以上的信号速率将在信号完整性上产生巨大挑战,以前低速可忽略的因素在高速通道中会严重影响传输性能,因此需要对通道中每个设计环节进行仔细分析。如图1所示,其信号链路中包含了多达10种的不同组件,从发送端开始依次为:发射芯片及封装过孔子卡走线发送端连接器背板及走线接收端连接器子卡走线过孔最后到接收

芯片。每一个组件均各自拥有其阻抗变化。

图1 背板示意图

信号在整个传输过程中,每个环节都会表现出信号完整性(SI)问题,例如插损、回损、串扰,从而大大降低系统性能[2]。

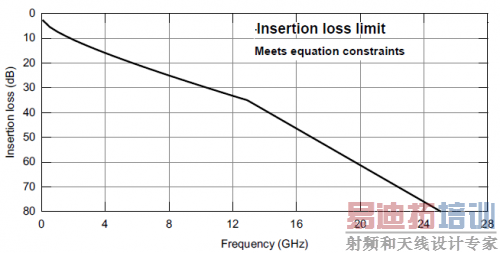

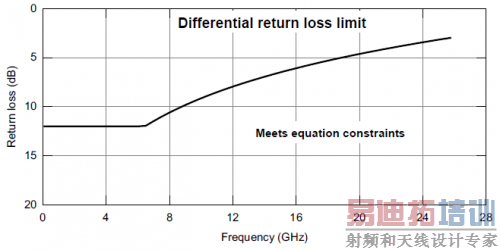

为了约束控制背板的损耗,IEEE的规范里对于背板的损耗都有严格的要求。根据100GBASE-KR4无源通道测试要求,测试范围为背板连接器一端到背板连接器另一端(规范定义为TP0~TP5),插损(IL)、回损(RL)满足如下公式[3]。

插损公式:

回损公式:

图2 通道插损要求

图3 通道回损要求

根据公式定义生成图2、图3模板,用于指导通道设计。规范中定义了总的通道插损必须小于35dB@12.9 GHz (包括前向纠错FEC),同时回损必须大于7.5 dB@12.9 GHz。连接器的设计必须满足总通道规范要求的同时,也要考虑其它因素例如走线、过孔以及芯片封装等也会给系统带来性能损失,还需要根据实际情况留有足够的设计余量。

3. 连接器介绍及分析

作为高速背板的"桥梁"与"枢纽",连接器的主要功能是连接子板与背板,传输高速差分信号或单端信号以及电流。高速连接器是二十世纪九十年代发展起来的,用于传输高速数字信号的一类新型连接器,其类型主要有ERNI公司的ZD 连接器、Tyco 公司的VITA 连接器、Amphenol 公司的LRM 系列连接器、FCI的XCede系列以及AirMax连接器、Molex的Impel系列连接器,等等。高速系统设计中,首要目标是信号传输路径阻抗连续并收发端阻抗匹配,从而保证信号反射(回损)最小[4]。另外连接器的管脚分布也会带来共模电感和寄生电容,影响到信号传输幅度(插损)以及差分对内偏斜。结合25G背板的使用场景,对于高速信号,连接器的选型必须满足如下技术指标:

(1)最大传输速率大于25.78125 Gbps,差分阻抗小于(100±10)Ω

(2)插入损耗IL小于3dB@12.89G,差分串扰≤-20 dB

(3)差分误码率:≤1012

为了能跟踪评测连接器各方面的参数性能,需要从连接器厂家获得连接器的S参数模型进行分析对比,本文将使用"SnpExpert"工具对S参数进行分析,该工具不仅能快速检查连接器参数的准确性,而且能非常方便智能的显示多端口S参数模型的插损回损,并与标准模板进行比较。

3.1 连接器插损分析

高速连接器受到绝缘介质材料、插针引线、管脚晶片以及电气结构等的影响,在信号传输时信号出现衰减,尤其是Ghz量级信号频率时,连接器的插针引线不能看作是理想的传输线(仅考虑对信号产生延迟),而是包含趋肤效应和介质损耗的有损传输线。另外,一个连接器存在多个通道,每个通道也会表现出不同的性能参数。为了了解连接器的整体性能及各个管脚的优劣,本文以使用SnpExpert工具导入8对差分pin连接器模型为例进行分析。软件自动生成对应端口及一键插损显示,减少繁复的多端口S参数设置,如下图4所示:

图4 连接器管脚插损

根据连接器要求,连接器在12.85GHz频率内插损控制在-3dB以内,图4中显示有两对pin插损达到了-5.6dB和-3.4dB,并不满足连接器要求,需要避免25G高速信号使用这两对pin。

3.2 连接器回损分析

高速连接器由于金属插针电镀、冲压、介质体的精密成型等因素,还要兼顾物理压接结构及拨插强度要求,连接器在传输通道中的阻抗并不连续,阻抗不连续会导致信号反射而产生回损[4]。如图5,连接器

图5 连接器pin脚示意图

pin设计成鱼眼压接结构或绞链结构。同样使用SnpExpert软件的时域分析工具,可发现个别管脚阻抗偏大,如图6的绿色曲线,达到了113Ω,而在高速连接器选择时,要求差分阻抗小于(100±10)Ω。

图6 连接器管脚阻抗

使用SnpExpert软件的模板功能,在软件中指定调用100Gbase-Kr4模块,输出回损曲线如图7,并增加了100Gbase-Kr4的模板比较功能(粉红色虚线)。回损曲线中,虽在12.87G位置没有超过-7.5dB,但部分通道非常接近标准限制,没有足够的设计余量。

图7 连接器管脚回损

3.3 连接器串扰分析

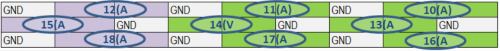

串扰由施扰信号传输方向相同的干扰(称为前向串扰FEXT) 和与施扰信号传输方向相反的干扰(称为后向串扰NEXT) 组成。通常管脚越密、并行越长,串扰越大。一个连接器存在多个通道,上节分析了每个通道性能参数多样性,由于连接器管脚设计密度偏高,这些通道的信号也会相互影响,即通道之间互相干扰。在实际应用中连接器管脚的排布对信号质量的影响是显而易见的,屏蔽高间距大的pin设计可以减少信号之间的串扰,提高信号质量。对于25G高速连接器,需要对高速信号对采用全屏蔽方式,从下图8可见,pin对之间并没有GND管脚包围,信号在连接器位置相互串扰。串扰是产生抖动、使波形失真的重要原因之一,严重影响信号质量[5]。系统要求差分串扰必须小于-20dB。

图8 连接器pin map示意图

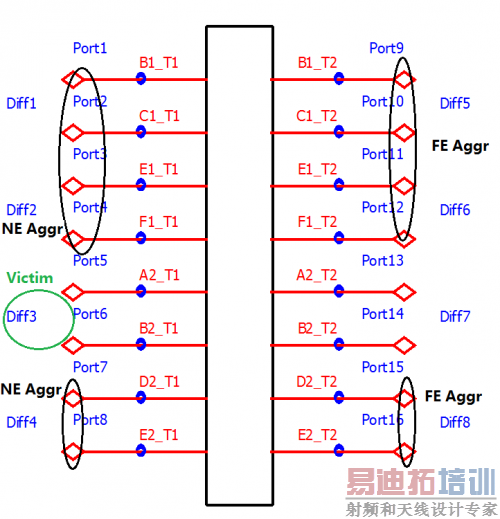

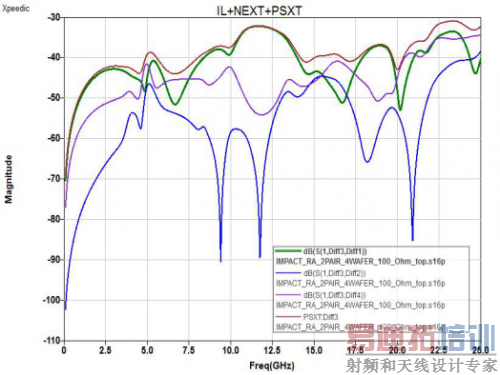

如图9, 在SnpExpert软件中指定Diff3为受害通道,其它通道为攻击通道。使用SnpExpert工具模拟串扰分析,图10为后向串扰(Next)的曲线,图11为前向串扰(Fext)曲线。可见,该连接器管脚分配使用上,满足小于20dB串扰要求。

图9 连接器串扰设置

图10 连接器后向串扰Next

图11 连接器前向串扰Fext

总结:

系统或仿真工程师在背板通道设计规划时必须对连接器的性能有足够的了解,才能很好的评估连接器的选型甚至连接器的管脚分配。本文先通过了解100GBase-KR4规范和系统要求,了解通道设计中阻抗连续、插损、回损及串扰的要求。由于SnpExpert工具的易用性和强大的模板功能,通过使用SnpExpert仿真工具对连接器的S参数模型进行分析评估,达到指导工程师分析连接器性能的目的。

文献:

[1]Eric Bogatin. Signal Integrity:Simplified[M]. Beijing:Publishing House of Electronic Industry,2009:10-14.

[2]Stephen H,Howard LH. Advanced signal integrity for high-speed digital designs [M]. New York: Wiley, 2009:19.

[3]IEEE 802.3bjl"/D1.3(Amendment of IEEE Std 802.3—2012),Draft Standard for Ethernet Amendment X:Physical Layer Specifications and Management Parameters for 100 Gb/s Operation Over Backplanes and Copper Cables[s].NY:IEEE Computer Society,2012—10—07.

[4]胡 军,李晋文,曹跃胜. Gbps串行链路信号完整性分析与设计 [J] .计算机工程与科学, 2009, 31-7:102-105

[5]胡军,李晋文,曹跃胜,杨安毅,张伟.差分对内偏斜对25 Gbps背板信号完整性的影响分析[J] .计算机工程与科学,2014.12:36-12

[6]SnpExpert--S参数显示和分析工具 workshop 培训手册