- 易迪拓培训,专注于微波、射频、天线设计工程师的培养

使用QDR-IV设计高性能网络系统之三

通过使用输入时钟(CK/CK#)可在上升沿和下降沿上对每个输入引脚进行采样。在输出时钟(QKA/QKA#)的上升沿上采样的输出值即为在输入时钟的上升沿上所采样的值。在输出时钟(QKA/QKA#)的下降沿上采样的输出值即为在输入时钟的下降沿上所采样的翻转值。在这种模式下,数据翻转无效,在进行地址/控制环回训练过程中,CFG#信号将为高电平。

图9. 环回训练框图

如图9所示,如果地址/控制信号未校正,DQA 上的信号(应在训练期间保持高电平)将变为低电平。该信号转换应由驱动信号的模块捕获,控制器则会对信号相应进行校准。

读取数据校正

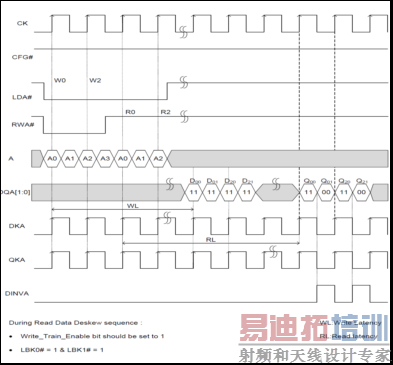

在该阶段,地址、控制和数据输入时钟都已经得到了校正。在读取数据校正过程中,用于写入存储器内的训练数据模型是一个常量值(D00,D01,D20,D21),如下面的波形框图中显示。在此训练序列中,LBK0#和LBK1#均被设置为1。

配置选择控制寄存器时,Write_Train_Enable 位将被设置为1。第一个和第二个数据突发均在同一个数据总线上被采样的,但第二个数据突发则在写到存储器内前完成采样的。Write_Train_Enable 位不会对读取数据周期产生任何影响。

将数据模型写到存储器内后,标准的读指令允许控制器访问这些数据,并会校正QK/QK#信号。当 Write_Train_Enable = 1 时,在写入过程中,DINVA/DINVB 将被忽略,在读取过程中,它将始终切换。

如下面的读取数据校正框图中所示,写入到存储器内的数据(D00、D01、D20、D21)全为1,相应的读取数据(Q00、Q01、Q20、Q21)则在1 和0 间切换。控制器必需捕捉到这些切换数据并进行验证。否则,控制器需要一个精确的校准来确认读取数据校正。

图10. 读取数据校正序列框图

在读数据校正序列中:

?设置Write_Train_Enable位为1

?LBK0# = 1 及LBK1# = 1

写数据校正

此时,地址、控制、时钟和数据输出都已经得到了校正。执行写入数据校正序列前,先再次进入配置模式,然后通过将相应位设置为0来禁用Write_Train_Enable。

在正常工作模式下,使用读指令后,通过使用存储器的写指令可校正写数据。所校正的读取数据路径用于确认器件是否已经正确地接收到写入数据。这样使处理器/FPGA能够校正下列与DK/DK#输入数据时钟有关的信号:DQA、DINVA、DQB和DINVB。

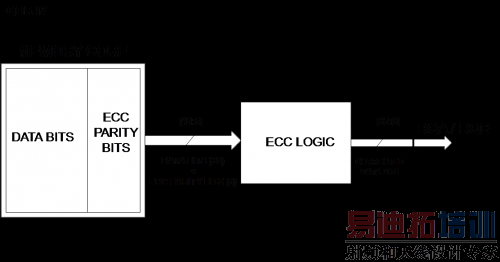

纠错码(ECC)

系统设计人员必需依赖片外纠错或冗余等技术提高可靠性。这些技术会增加PCB空间或处理时间方面的开销。QDR-IV是一个单芯片解决方案,引入了片上纠错码(ECC),从而节省了空间和成本,降低了设计复杂性。此外,它还降低了QDR-IV存储器阵列的总软失效率(SER)。该特性可应用于数据总线宽度为x18和x36的选项,并在SRAM中始终被启用。ECC保护提供了单比特纠错(SEC)。

QDR-IV从输入数据生成ECC奇偶校验位,并将它们存储在存储器阵列中。存储器阵列包含用于存储ECC奇偶校验的额外位。但是,不会将这些额外的内部校验位用于外部引脚。

例如,图11显示的是x36器件的输出数据逻辑框图。36数据位需要6个ECC校验位;存储器内核会将42位(36个数据位 + 6个 ECC校验位)传输到ECC逻辑内。因此,ECC逻辑会提供已纠正的36位输出数据。

无ECC位的QDR/DDR SRAM的SER故障率(FIT)通常为200 FIT/Mb。但带有ECC时,该数值将为0.01 FIT/Mb,提高了4个数量级。

图11. 输出数据逻辑(x36器件)

QDR-IV存储器控制器的设计建议

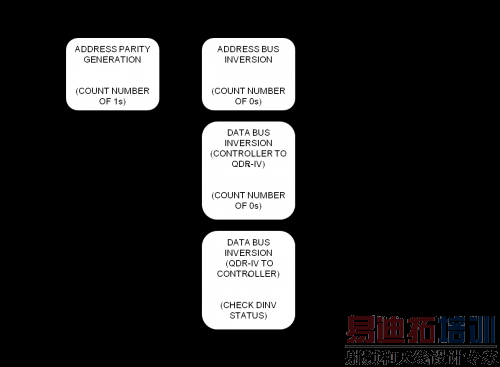

本节提供一些存储器控制器启用QDR-IV的地址奇偶校验和总线翻转功能的设计建议。

存储器控制器首先要根据地址总线生成地址奇偶。然后,需要在地址总线和地址奇偶位上进行地址翻转。

对于数据总线转换,将数据发送给QDR-IV前,存储器控制器需要计算每个DQ总线上的逻辑"0"的数量,以便生成相应的DINV位(取决于数据总线翻转条件)。

将数据发送给存储器控制器时,QDR-IV使用相同的数据总线翻转逻辑。为了识别QDR-IV的接收数据,控制器仅要检查相应DINV位的状态。如果控制器接收DINV = 1,需要翻转相关的数据总线;否则,保持接收到的数据位不变。

图12显示的是存储器控制器的设计注意事项。

图12. 存储器控制器的设计注意事项

结束语

QDR-IV提供2132 MT/s的最大RTR,是市场上性能最高的标准化解决方案。凭借较高的RTR外加两个双向端口、ECC、总线翻转、ODT、地址校验等差异化特性,它已成为网络系统的首选解决方案。QDR-IV的优势还适用于其它需要较高RTR和信号完整性的系统,如高性能计算和图像处理系统。

上一篇:英特尔基带肆意挑衅,这些基带大佬谁最担心?

下一篇:能把Wifi

HaLow干翻,蓝牙5.0才是IOT最佳选择?