- 易迪拓培训,专注于微波、射频、天线设计工程师的培养

系统解读无线通信之SDR和CR

软件定义无线电(SDR)过去是比较少有的舶来品。不过现在,大多数现代无线电都采用软件定义无线电的架构和技术。随着每年IC和其他技术的不断进步,SDR的性能和应用范围都在与日俱增。事实上,认知无线电(CR)等新兴技术的出现,为SDR在无线通信领域大显身手创造了条件。

什么是软件定义无线电

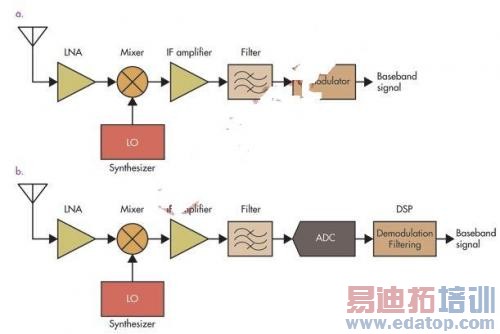

软件定义无线电使用软件来执行接收器和发射器中的部分信号处理任务。例如,采用随处可见的超外差架构的传统接收器通过基本电路(图1a)执行所有的信号处理任务。这种超外差架构将输入信号通过降频转换成中频(IF)信号,以便进行解调和其他处理。

图1:常见的传统无线电接收器(a)将标准模拟超外差架构与执行所有功能的模拟电路配合使用。高级超外差接收器(b)将数字解调技术与DSP配合使用。

早期的软件定义无线电接收器(图1b)在中频级之后用模数转换器(ADC)替代了解调器,并在数字信号处理器(DSP)中执行解调和部分滤波工作。如今,由于ADC采样速率的提高,DSP可以处理更多的功能。

要使DSP工作,信号的振幅和相位必须是已知的,从而催生了一种将接收到的信号分至两个通路的架构,一个通路产生同相(I)信号和一个通路产生90°相移正交(Q)信号。基本载波信号具有以下形式:

V = Ac cos(2πfct +φ)

其中,fc是载波频率,φ是相位,Ac是载波振幅。这些参数中的任何一个参数都随调制方式的不同而有所不同。对于数字领域中的解调而言,单信号对于现有的算法来讲是不够的。因此,经过调制的信号被转换成I信号和Q信号:

V = I(t) cos(2πfct) + Q(t) sin(2πfct)

正交信号的任何振幅、频率或相位变化都可以检测到,并用于解调或其他过程中。

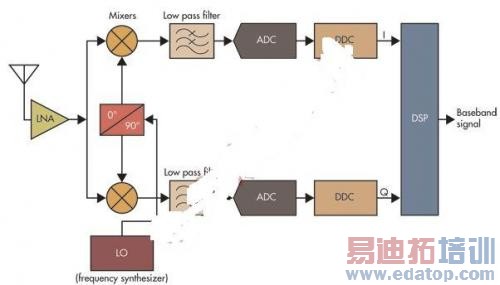

图2是一个现代I/Q软件定义无线电接收器的框图。低噪声放大器(LNA)一般会增强来自天线的输入信号,然后该信号再被施加至两个混频器。混频器逐步产生I信号和Q信号。两个混频器都从锁相环(PLL)频率合成器中接收本振(LO)信号。请注意LO信号与两个混频器之间的90°相移。

图2:现代软件定义接收器采用I/Q架构将信号分成两个正交通路。需要I和Q通道通过数字信号处理算法恢复各种类型的调制。

LO频率被设置成信号频率,因此在不调制的情况下混频器的差分信号为零。进行调制时,差分信号为基带信号或原始调制信号。这种架构被称为直接转换或者零中频。

基带信号在低通滤波器中进行滤波以消除混频器输出端的和分量之后,此信号在一对ADC中被转换成数字信号。然后数字基带信号通过数字下变频器(DDC)的处理,降低采样速率,以便能够与数字信号处理电路兼容。然后数字信号处理电路根据应用的要求,同时使用I信号和Q信号进行解调、均衡和额外的滤波。

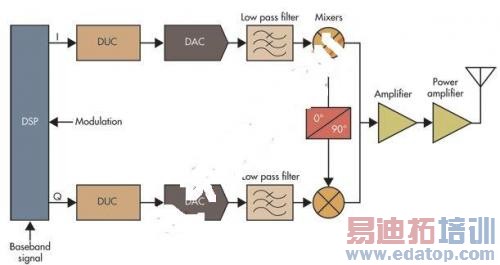

在现代软件定义无线电发射器中,DSP调制器将要传输的数据划分成I信号和Q信号,并将这些信号馈至数字上变频器(DUC),以提高其采样速率(图3)。I信号和Q信号接下来会被发送至数模转换器(DAC),从而产生最终的基带信号。然后这些基带信号会进行低通滤波,并被发送至混频器,混频器将该信号升频至最终的发射频率。该信号最后会发送至功率放大器,然后再施加至天线。

图3:在SDR发射器中,调制是在DSP中进行的。然后,I/Q架构产生两个正交信号,这两个正交信号合并在一起,然后升频至最终的频率以便进行传输。

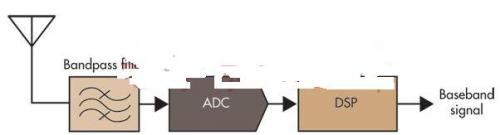

所有的现代软件定义无线电收发器都采用这里所示的接收器和发射器电路的某种基本变体。当然,随着ADC和DAC采样速率的日益增加,数字处理越来越向天线靠近。最终的接收器会成为天线端的一个滤波器,以限制带宽和LNA,然后再进行快速的ADC处理(图4)。然后,DSP执行解调和滤波等所有的其他处理。覆盖频率高达30MHz的商用业余无线电和短波接收器已经开始使用这种先进的架构。

图4:最终的SDR接收器仅采用一个输入带通滤波器、一个ADC和一个DSP。所有的解调、滤波和其他功能都在DSP中进行。

以下的许多功能现在都是以数字方式执行的:

滤波(低通、高通、带通和带阻)、调制(AM、FM、PM、FSK、BPSK、QPSK、QAM、OFDM等)、解调、均衡、压缩、解压、频谱分析、预失真。

新的调制方式和相关过程通常被称为波形。通过更改波形软件,用于像FM语音这样的单个应用的无线电可以针对具有不同协议的不同频率上的高速数据重编程序。

软件定义无线电的优势在于硬件越来越简单。标准RF电路得到了最大限度的缩减,从而保证了低IC成本。DSP软件提升各种功能(比如滤波器)的性能,从而实现比同等模拟电路更好的性能。数据信号处理还可以对RF器件的某些不足进行补偿。

此外,重编程序可以提供各种灵活性,包括修正错误、增加新功能、包含升级的操作以及提升性能等。可以通过软件快速更改具有灵活设计的软件定义无线电,从而整合新的调制方式、新协议以及一般需要新硬件的其他重大调整。

软件定义无线电的不足之处在于软件复杂性、开发成本和开发时间、某些应用的频率范围有限以及往往较高的功耗。

软件定义无线电的硬件

软件定义无线电需要快速ADC、DAC和DSP。多年来,ADC的采样速率一直都在与日俱增,现在已经达到了千兆赫的水平。许多软件定义无线电采用低中频架构和ADC,将许多100 Msamples/s的采样速率提升至几百Msamples/s,甚至更高。