- 易迪拓培训,专注于微波、射频、天线设计工程师的培养

利用中端FPGA实现低成本网络

从网络的核心模块到边缘设备,都在经历着巨大的变革。无线市场与其数千万的"永远在线"连接、下一代回程通信的巨大传输压力,以及各种为使用现有有线通信基础设施的消费者提供宽带通信的举措,都是推动网络发展的关键因素。因此,网络核心朝着100及400Gbps的数据通道发展;网络中心区域也从10Gbps升级为100Gbps,用以支持不断扩展的各种网络接入标准、协议和接口。此外,为支持日益增大的用户流量需求并降低总体传输延迟,接入网络也正在从之前的并行接口升级到现代高速串行接口。

由于网络运营商们期待以低成本提升网络容量,并同时保持总体覆盖率,因此他们往往不可能彻底更换目前已经安装好的硬件设施。产品上市时间、整体的升级费用和现有软件支持上的投入,仅仅是几个必须考虑的问题。当设备升级时,必须提供必要的 "翻新" 以延长使用期限,同时加入符合预期网络需求的功能特性,许多NEP(网络设备供应商)发现具有收发器功能的中端FPGA是一种十分有效的解决方案。

中端FPGA是相对较新的一类FPGA。这些成本和功耗优化的器件提供了传统现场可编程门阵列的所有特性,并结合了仅高端器件才具有的各种先进功能。例如,这些可编程器件提供了具有成本效益且功耗优化了的串行接口(SERDES),这使他们能够弥补现有的和下一代通信解决方案之间的差距。带串行接口的中端FPGA也可以配置为支持各种数据传输速率和接口标准,无论是否是行业标准的还是专用的。并且,由于同一种规格大小的器件不可能符合所有的需求,因此这些器件的SERDES通道数量随不同型号而变化,从而使得设计工程师能够优化其可编程解决方案,以满足特定的成本和功耗目标。

中端FPGA中串行接口的可配置功能是十分关键的,它赋予了这些器件独特的竞争优势。虽然过去很多网络设备供应商可能会考虑采用其"自行开发"的接口标准,尤其是在整个机架的设备已经由同一制造商开发的情况下,但当今市场拥有多样化的选择,并且供应商设备之间的互操作性已成为必然。大型的系统供应商仍将继续提供完整的解决方案,而其他制造商则寻求能够在行业标准机箱内工作的差异化解决方案,或者独立的"薄型设备"。实现行业标准串行接口不仅可以减少系统设计时间,还能够改善不同供应商之间的互操作性,提高整个系统的可靠性,并拓宽供应商设备的接纳范围。

在实现串行接口时,一个重要的特性是能够创建可扩展的数据链路,以满足传输带宽的要求。为使带宽与所支持的传输协议相匹配,中端FPGA加入了硬化的PMA和PCS逻辑模块,它们在功能上可以邦定在一起。邦定机制实现了多个收发器通道来支持一个协议,而其余的串行接口仍可以独立地支持其他协议,或者被禁用,从而进一步节省整个系统的功耗。虽然收发器通过加入PMA和PCS功能模块提供物理层接口,但还需要在更高的"客户"层提供大量额外的逻辑,以创建一个完整的行业标准解决方案。虽然ASSP可以提供带有硬化串行接口的特定接口解决方案,但是它们缺乏必要的灵活性,无法支持网络接入市场中用到的各种接口。

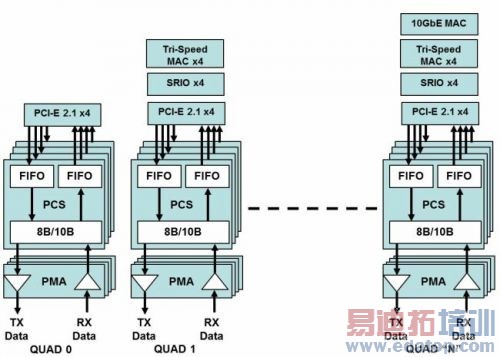

此外,基于SERDES的高端FPGA也可以被设计为在其结构内包含大量的串行传输逻辑,只是代价高昂:额外的设计和验证时间、更多的功耗和尺寸大小。此外,中端FPGA还为电路板级和系统级设计人员提供了另一个关键优势。通过为FPGA的软逻辑阵列增加一定数量收发器(根据不同的器件),以及硬化的行业标准传输协议逻辑,这些器件提供了一个灵活、低成本和小尺寸的通信解决方案。如图1所示,通过选择适当的FPGA,可以很容易地实现不同的传输协议解决方案。

图1:具有收发器功能的中端FPGA。

接入网络由来自不同网络运营商提供的基础设备构成。并且,由于预计将会有大量的陈旧设备仍将在之后几年继续使用,越来越多的运营商转而使用一种全分组(all-packet)网络。随着向全分组网络发展,一些行业标准技术正在迅速成为控制平台和数据传输互连的主导。以太网以其悠久的历史、使用的广泛性以及本地IP数据包支持,将主导下一代网络。而PCI-Express凭借广泛用于计算、服务器和消费电子市场,也正在大量用于器件级和背板互连,同时还被广泛部署用来取代并行PCI总线。串行无线IO标准则被用于各种无线、DSP和其它嵌入式计算解决方案。如上所述,许多中端FPGA支持这些关键标准,从而为设备制造商提供了一系列丰富的硬化解决方案。除了成本和功耗上的优势,这类器件还无需实现和验证通信协议,这使得设计人员能够专注于在FPGA结构内实现自己的差异化解决方案和系统升级功能。

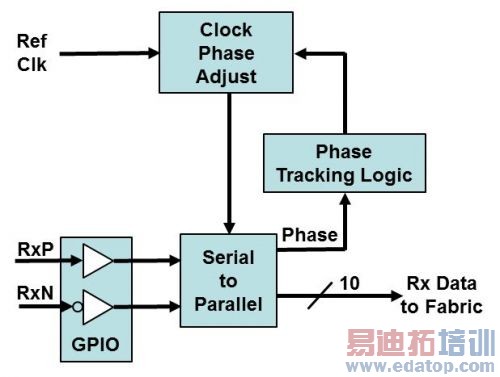

升级为全分组网络时的一个重要元素是能够将网络最边缘处具最低数据带宽需求的数据接口和网络中心区域及核心区段更高数据传输速率的接口汇聚在一起。边缘路由器、接入交换机和其他网络汇聚设备都同时支持低和高带宽数据速率。为满足数据汇聚的要求,中端FPGA不仅为下一代高速串行接口提供了一种经济的解决方案,还通过其增强的通用I/O(GPIO)功能支持传统的串行接口。利用GPIO来支持低端串行线速率,即1.25Gbps或更低,使得较昂贵的集成收发器通道可用于更高的串行线路速率。为支持串行接口,必须有一些时钟和数据恢复(CDR)逻辑,这是中端FPGA的另一个特点。图2提供了一个典型的CDR电路模块图。

图2:典型CDR电路模块图。

通过将硬化的时钟和数据恢复(CDR)逻辑合并到I/O结构中,再加上可访问选择硬化传输协议内核的PCS接口的结构,中端FPGA为各种不同的汇聚设备接口提供了串行线速率支持。

对设计人员而言,应用层逻辑是在FPGA中实现其解决方案时需要考虑的另一个因素。大多数传输协议都必须支持多种数据类型,每种都有其自己的传输模式、服务质量标准和控制平台要求。因此,硬化逻辑必须支持各种客户层协议语义。为提供最符合成本效益的和完整的解决方案,中端FPGA以软逻辑模块的形式提供这些不同的逻辑层接口。这些软逻辑模块为底层的传输协议模块提供了无缝接口,因为它们是整个协议栈的一部分,符合各自的行业标准。

上一篇:揭秘无线WiFi

802.11系列标准家族

下一篇:高速铁路的CDMA覆盖关键