- 易迪拓培训,专注于微波、射频、天线设计工程师的培养

基于VXI总线的射频开关模块

0 引言

随着电子装备的现代化、高科技化和复杂化,要求对电子装备进行现场快速测试,这就必须依靠自动测试系统来完成。为了提高我军的装备保障水平,必须尽快实现我军军用自动测试设备(Automatic Test Equipment,简称ATE)的国产化,缩短与国际先进水平的差距,确保军用检测设备免受国外技术保护的限制,提高军用ATE的效费比。因此研究VXI总线技术,开发满足军方特殊要求的VXI总线模块,具有十分重要的意义。

射频开关是用于控制射频信号传输路径的控制器件之一,在无线通信、电子对抗、雷达系统、自动测试设备等许多领域中有广泛用途。随着现代无线通信系统的发展,移动通信、雷达、卫星通信等通信系统对收发切换开关的开关速度、功率容量、集成性等方面有了更高的要求。

1 VXI总线接口电路的设计与实现

VXIbus是VMEbus在仪器领域的扩展(VMEbus Extensions for Instrumentation),是计算机操纵的模块化自动仪器系统。它依靠有效的标准化,采用模块化的方式,实现了系列化、通用化以及VXIbus仪器的互换性和互操作性,其开放的体系结构和Plug&Play方式完全符合信息产品的要求。它具有高速数据传输、结构紧凑、配置灵活、电磁兼容性好等优点,,因此系统组建和使用非常方便,应用也越来越广泛,已逐渐成为高性能测试系统集成的首选总线[1]。

VXI总线是一种完全开放的、适用于各仪器生产厂家的模块化仪器背板总线规范。VXI总线器件主要分为:寄存器基器件、消息基器件和存储器基器件。目前寄存器基器件在应用中所占比例最大(约70%)。VXIbus寄存器基接口电路主要包括:总线缓冲驱动、寻址和译码电路、数据传输应答状态机、配置及操作寄存器组四个部分。四个部分中除总线缓冲驱动采用74ALS245芯片来实现外,其余部分都用FPGA来实现。采用一片FLEX10K 芯片EPF10K10QC208-3和一片EPROM芯片EPC1441P8,利用相应软件MAX+PLUSⅡ来进行设计与实现。

1.1 总线缓冲驱动

该部分完成对VXI背板总线中的数据线、地址线和控制线的缓冲接收或驱动,以满足VXI规范信号的要求。对于A16/D16器件,只要实现背板数据总线D00~D15的缓冲驱动。根据VXI总线规范的要求,此部分采用两片74LS245实现,用DBEN*(由数据传输应答状态机产生)来选通。

1.2 寻址和译码电路

寻址线包括地址线A01~A31、数据选通线DS0*和DS1*、长字线LWORD*。控制线包括地址选通线AS*和读/写信号线WRITE*。

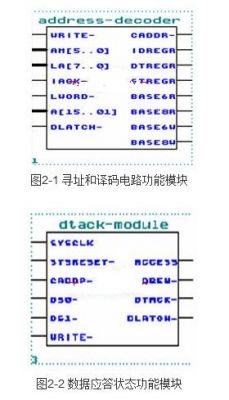

本电路的设计采用MAX+PLUSⅡ的原理图设计方式。利用元件库里的现有元件进行设计,采用了两片74688和一片74138。其创建的功能模块如图2-1所示。

该功能模块对地址线A15~A01及地址修改线AM5~AM0进行译码。当器件被寻址时,接收地址线及地址修改线上的地址信息,并将其与本模块上硬件地址开关设置的逻辑地址LA7~LA0相比较,如果AM5~AM0上逻辑值为29H或2DH(由于是A16/D16器件),地址线A15、A14均为1,并且A13~A06上的逻辑值与模块的逻辑地址相等时,该器件被寻址选通(CADDR*为真)。接着其结果被送往下一级译码控制,通过对地址A01~A05进行译码选中模块在16位地址空间的寄存器。

1.3 数据传输应答状态机

数据传输总线是一组高速异步并行数据传输总线,是VMEbus系统信息交换的主要组成部分。数据传输总线的信号线可分为寻址线、数据线、控制线三组。

该部分的设计采用MAX+PLUSⅡ的文本输入设计方式。由于DTACK*的时序比较复杂,所以采用AHDL语言来进行设计,通过状态机实现。设计的功能模块如图2-2所示。

该功能模块对VXI背板总线中的控制信号进行组态,为标准数据传输周期提供时序及控制信号(产生数据传输使能信号DBEN*,总线完成数据传输所需的应答信号DTACK*等)。在进行数据传输时,系统控制者首先对模块进行寻址,并将相应的地址选通线AS*,数据选通线DS0*、DS1*以及控制数据传输方向的WRITE*信号线等设置为有效电平。当模块检测到地址匹配及各控制线有效后,驱动DTACK*为低电平,以此向总线控制者确认已经将数据放置在数据总线上(读周期) 或已经成功地接收到数据(写周期)。

上一篇:基于数字RF调制器的有线网络融合方案

下一篇:国民技术死守2.4G移动支付技术?