- 易迪拓培训,专注于微波、射频、天线设计工程师的培养

基于TI KeyStone SoC的多标准无线基站实现

TeraNet—TeraNet采用层级交换结构,能够在SoC内组合交付超过2Tb的数据传输带宽。这从本质上确保了内核或协处理器再也不会缺少数据,并能够交付名符其实的处理能力。由于交换结构属于层级式而非常平坦的纵横式,因而整体功耗能够在空闲状态下大幅降低,并能以最小的时延提供非常高的性能,这也是新一代基站的关键要求。

多核共享存储控制器(MSMC)–MSMC是一种可用于增强性能的独特存储器架构。MSMC允许内核在不使用任何TeraNet带宽的条件下直接访问共享存储器。MSMC可在各内核和其他IP模块之间对共享存储器的存取进行判优,从而消除了存储器争用的情况发生。DDR3外部存储器接口(EMIF)可直接连接至MSMC,从而不仅可减少与外部存储器获取相关的时延,而且还能提高速度并支持基站应用的需求。

超链接—超链接是一个具有50Gbps总吞吐量的互连协议,其可实现高速度的低协议层通信以及与其他KeyStone、FPGA或ASIC设备的互连互通,并能够提供从主器件到同伴器件的透明的存储器映射接入。这就能够大幅简化软件编程,并为OEM厂商实现可扩展的解决方案提供了无缝路径。

这一系列功能强大且高度灵活的SoC组件是设计高效率多标准基站的关键。鉴于2G、3G、4G系统之间存在各种复杂性,频分复用系统对时分复用系统的挑战性以及区域部署的多变性,若不从一个坚实的基础开始,想要在所有的平台上使用通用的SoC等于纸上谈兵。

TI的加速战略为了多标准能成功实现,第二大关键因素就是是否能够通过TI的加速战略。DSP始终是无线基站基带处理的关键元素。其对信号处理的优化非常适用于无线应用领域。尽管如此,出于成本和功耗的原因,一些常规和标准定义的功能更适用于在硬件中实施。虽然这些可以在外部硬件逻辑器件中完成,但TI还是为基站制造商提供了更低成本及更低功耗的备选方案,即在基于KeyStone的SoC中集成了这些功能。自2003以来,TI一直致力于为无线基站市场提供基于DSP的集成型SoC。随着硅芯片技术的不断发展以及无线标准的不断演进,公司不断推出新生代产品,从而可为OEM厂商提供能满足运营商需求的最具竞争优势的解决方案。

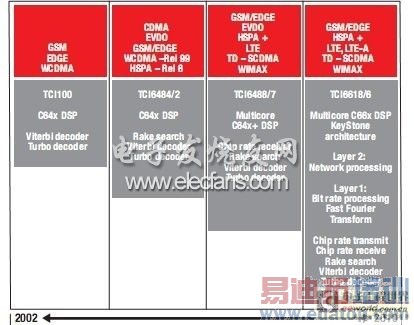

图2显示了TI在无线基站SoC领域的发展历程和领导地位。第一代SoC承担了GSM和CDMA等早期2G技术的无线部署,其中包含了viterbi和turbo解码器。随着无线标准不断进步,超越语音服务而进入数字时代,TI为实现更高容量增强了DSP及相关协处理器。第三代SoC能够实现更丰富的功能,其中包括支持所有标准的第一代带无线协处理器的多内核DSP,以及对集成了接收加速器的WCDMA(WCDMA在全球范围内的应用不断增加)的更全面支持。

当今的第四代和目前解决方案系列可为所有3G、4G添加一系列广泛而强大的协处理器,从而加强现有无线标准的性能。这些协处理器包括多种特性,如WCDMA的传输发射、所有标准的比特速率处理、快速傅里叶变换,以及功能更强大的turbo解码等。除了支持物理层及所述标准中的第一层外,目前这一代SoC还包括对第二层功能以及网络协处理器的支持。

图2–-TI的实施历程:基站SoC中的无线标准

TITMS320TCI6618是一款最新推出的基站SoC,其基于KeyStone平台之上,拥有DSP周期数相当于超过250GHz的专用标准可配置硬件加速器。这些加速器可支持现行的所有通用无线标准,其中包括GSM、WCDMA、TD-SCDMA、WiMAX以及LTE等。这些协处理器的实施是基于成熟且会消耗大量处理周期的标准功能而精心挑选的。如欲了解有关最新器件中加速功能的更多详情,敬请参阅TI的白皮书《采用TI多标准基站SoC实现卓越的性能、效率和差异化功能》。

在技术发展的每一个阶段,TI都始终稳居业界领先无线基站SoC供应商的地位。采用TI技术进行高灵活性的可行部署,用户能够在缩短学习周期方面拥有独特的优势。在每个最新发展的工艺节点,都离不开新技术的推出,而且现有技术的增强都是基于现实世界的丰富经验及应用反馈进行的。作为TI当前采用的SoC,TCI6488已拥有数百万片的出货量,而且被全球逾200家运营商所广泛采用。其是迄今为止,本行业领域内部署最广泛的3G无线基站SoC。在提供作为SoC一部分且基于标准的现场固化加速器功能方面,TI拥有独特的优势,能够帮助OEM厂商显著降低风险。

总结毋庸置疑,部署多标准基站是获得成功至关重要的因素,能够让无线运营商所面临的挑战迎刃而解。这些通用平台将使得在向未来新技术进行升级时无需进行重大改进或重新进行设备部署。不断进步的基站制造商在努力解决运营商所遇困难的同时也在不断实现其自己的业务目标。

推荐阅读:

TI KeyStone II多核SoC概述。TI 最新KeyStone多核SoC集成 TI 定浮点 TMS320C66x 数字信号处理器 (DSP) 系列内核(可实现业界最佳的单位功耗性能比)与多个 ARM Cortex-A15 MPCore处理器(可实现前所未有的高处理性能与低功耗),可推动各种基础架构应用发展,实现更高效的云体验。

TI KeyStone II SoC详细介绍。摘要:TI's KeyStone II Multicore Architecture provides a unified platform for integrating RISC and DSP processing cores.

KeyStone II多内核处理器Navigator Runtime应用案例分析。摘 要:多内核 处理器给编程人员带来了新的挑战。在多内核项目中,半数以上的成本来自软件开发。多内核编程的具体挑战是非对称多内核处理器 (AMP),因为其中相同的器件中驻留着 RISC 与 DSP 内核等不同类型的处理单元。这主要是因为操作系统 (OS) 对资源管理与负载均衡的支持非常薄弱甚至根本没有,导致可扩展性差与资源利用率低。

上一篇:IP地址管理常见功能解析

下一篇:微距条件下的无线传能的实现