- 易迪拓培训,专注于微波、射频、天线设计工程师的培养

FPGA研究设计平台为网络发展加速

使用不断变大的比特流位宽来配置FPGA,如果器件的配置时间超过PCIe的限制,可能就会出现问题。V5TX240T就会遇到这样的问题:平台闪存器件的存取速度远远低于V5TX240T理论上能够处理的速度,从而带来了瓶颈。作为应对措施,设计人员可以考虑配置部分比特流,并通过并行方式存取平台闪存器件,从而以最大速度配置FPGA。为了提高实现的可能性,我们为板卡配备了两个平台闪存器件,可以通过CPLD连接到FPGA的配置接口。此外,该板卡还支持标准的JTAG编程接口。

FPGA设计

构建成功的开源库的一个关键因素是严格的架构规范以及标准的、抽象且定义准确的接口。实际上,我们认为这些接口对提供一个能够轻松地将大型全球性社区贡献的组件组合在一起的构建块系统具有重要的意义。标准化保证了物理兼容性,物理连接功能之外的清晰定义避免了对接口协议的误解。在理想的情况下,用户可以不对实施内在的知识做详细了解,就可以部署抽象组件。

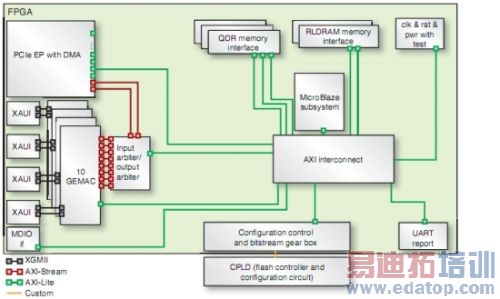

作为完整平台发布的一部分,我们将提供完备的架构规范和带有关键组件的参考设计。这些关键组件包括:

OpenCPI的PCIe端点;

4个XAUI LogiCORE IP模块和4个10G模式下的10GEMAC LogiCORE内核(后者许可协议下使用);

2个基于XAPP852的RLDRAMII存储器控制器;

3个基于MIG3.1的QDRII存储器控制器;

用以检查时钟频率和加电完毕信号,并生成所有所需系统时钟的时钟及复位模块;

针对1G运行模式的三态以太网MAC(TEMAC);

用于配置物理层器件的MDIO接口;

带有能够处理所有管理任务的支持系统的MicroBlaze控制处理器;

UART接口;

配置控制和比特流工具箱,为平台闪存器件提供编程路径;

可将所有输入流量整合成一个数据流的输入仲裁器;

可将流量分配给指定的输出端口的输出仲裁器。

图3显示了这些组件如何互联,以支持10G业务。对数据传输,我们选择了AMBA 4 AXI串流协议。对控制流量,则选择了基于AMBA4 AXI-Lite的接口。

图3:面向10G业务的FPGA设计架构基于AXI协议。

发展现状与未来展望

NetFPGA-10G板卡的设计验证已经完成。一旦完成产品测试平台开发,该板卡可立即投入生产。目前正在进行FPGA的初步设计和首次发布相关代码。