- 易迪拓培训,专注于微波、射频、天线设计工程师的培养

面向3G LTE基站设计的预处理解决方案

4. LTE基带处理的重要特征

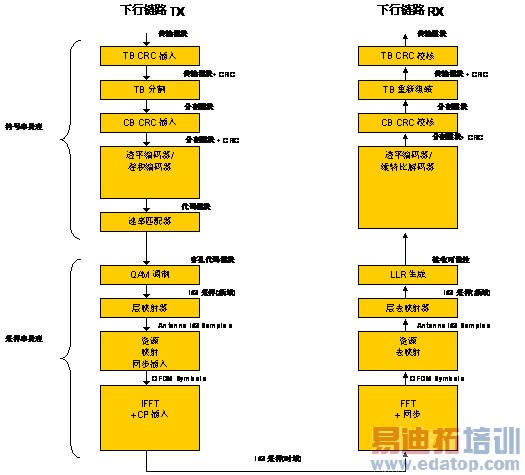

针对Tx和Rx的下行链路物理层如图3.0所示。注意,它可以被分解为两类处理,即符号率处理和采样率处理。从图3.0可见,与基于WCDMA的UMTS标准相比,符号率处理比较简单。

图5.0 3GPP LTE 下行链路处理

正如在UMTS中一样,LTE基站设计所面临的挑战在于上行链路的处理。在LTE的情形下,这进一步结合了短的处理时间要求,以实现较低的延时,与此同时,在Node B具有较之于RNC更高层的功能。

在这一节我们将从微观和宏观两个方面回顾各种挑战以及解决方案。

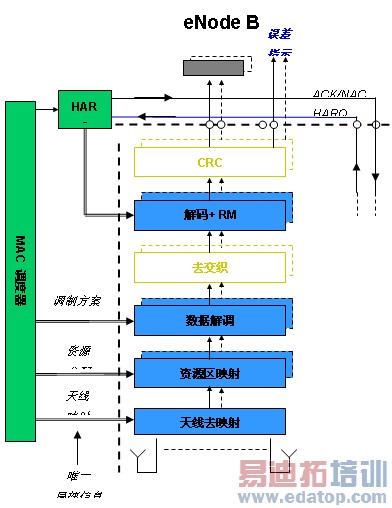

在微观层面,特别是对于如图6.0所示的上行链路信号链来说,LTE延迟预算主要由HARQ往返的8ms延时来定义,也就是说,最初传输与再次传输之间的时间。要考虑两倍1ms的一次传输时间,刚好把6ms留给发送和接收数据。那意味着LTE上行链路处理必须在3ms 以内满足由下列功能提出的延迟预算。它们分别是:

• 信道估计延迟;

• 解调;

• 速率匹配和IR组合;

• 透平(Turbo)解码;

• MAC/RLC处理;

• UL/DL时间偏移量。

图 6.0 LTE 上行链路信号链

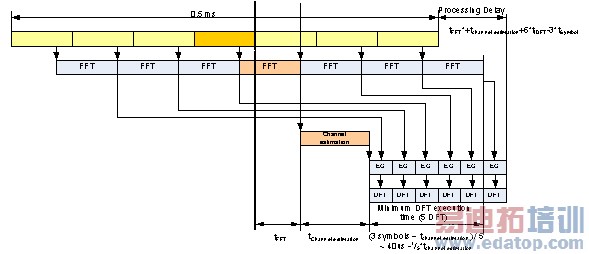

假定需要短的处理时间,因此,至关重要的是诸如iDFT这样的、在SC-FDMA解调中所使用的重要模块,以及透平解码必须在尽可能最短的时间内完成。赛灵思提供IP核解决方案,使基站设计工程师能够达到iDFT以及透平解码(Turbo Decoding)应用的目标。

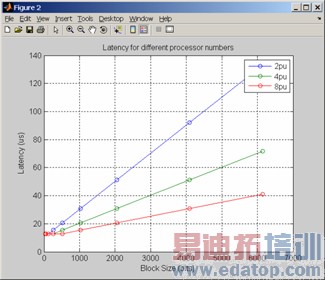

以如图7.0所示的iDFT处理为例,经过信道估值,在最坏情形下iDFT处理可用的最大处理时间是40us。赛灵思的iDFT解决方案使所有12的倍数的点长具有由2、3和5构成的素因子,能够满足处理时间的要求。除了FFT/iFFT之外—两个处理用DSP或FPGA均有效,在FPGA中做iDFT有明显的优势,因为DSP的比特反向寻址仅仅适合于基数2。类似地,为了有效地并行实现解码,赛灵思面向具有QPP交织器的LTE的透平解码IP核,利用400MHz的时钟速度对如图8.0所示的最大代码模块长度进行8次迭代的情形仅仅花40us的解码时间。

图7.0 LTE 上行链路 iDFT处理要求

图8.0赛灵思透平解码器的性能与模块大小及处理单元数量的比较

上一篇:NGN的定义及发展

下一篇:如何使用Cisco路由器配置实现VoIP