- 易迪拓培训,专注于微波、射频、天线设计工程师的培养

基于SoC的实时信号处理系统中存储系统

录入:edatop.com 点击:

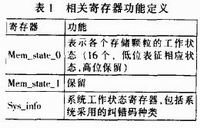

数据重组和地址重新生成

该纠错容错逻辑采用了多种方法进行容错,主要包括采用行冗余模块实现容错、降低纠错能力进行容错、将用于纠错的模块用于容错等。当自检模块发现存储颗粒出现故障时,将Mem_state寄存器的相应位置为1。而存储系统的数据组合以及地址生成都是与Mem_state寄存器相关的可配置逻辑。

(1)采用行冗余模块实现容错。当自测逻辑发现某个颗粒出现故障时,首先选择采用行冗余模块进行容错的方法。CS片选信号可以看作地址信号的一部分,当寄存器Mem_state中存在一位为1,则出现故障的颗粒所在的存储颗粒行就会被关闭(拉高CS信号),同时打开冗余行(拉低CS信号),其他信号不变。

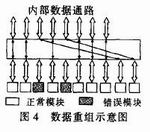

(2)将用于纠错的模块用于容错。当自测逻辑发现某个颗粒出现故障且所有的冗余行都已经启用,可以适当将纠错的模块用于容错。这时需要在地址方面和数据重组方面都进行一定的改动,主要包括:①在故障颗粒所在的行内,故障颗粒的地址和数据都被转发到空闲颗粒。②所有的数据线依然直接与控制器模块相连,但在模块内部,数据重组逻辑自动将冗余颗粒的数据通路重组到故障颗粒的数据通路上来。③纠错码编解码逻辑自动调整编解码方案。根据相关寄存器的值,纠错码的编解码逻辑自动降低纠错能力,数据重组逻辑也自动定向纠错码的数据通路。图4为数据重组示意图。

系统纠错容错能力分析

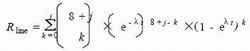

假设各个DDR颗粒之间发生错误的概率是互相独立的,设每个颗粒发生错误的概率恒定为λ,则每个DDR颗粒的可靠性符合泊松分布,其可靠性为Rm=e-λt。在Mem(i,j)系统中,每行的可靠性为

整个系统的可靠性为

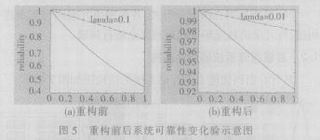

重构前后系统可靠性的变化如图5所示。

由此,可以根据故障概率λ计算出系统的整体可靠性Rsystem,根据系统要求的可靠性可以反向计算出所需要的i,j,从而构建出完整的Mem(i,j)容错存储系统。

结论

针对SoC实时数字信号处理系统的特点,设计了一种新的具有自适应容错纠错能力的二级冗余存储体系结构。详细论述了系统在存储颗粒组织排列和信号连接方面对于纠错容错能力的支持、系统在逻辑设计上对纠错容错能力的支持等。新的存储系统容错方案可以有效地提高存储系统的可靠性,下一步的工作将集中在整个系统的低功耗优化方面。

该纠错容错逻辑采用了多种方法进行容错,主要包括采用行冗余模块实现容错、降低纠错能力进行容错、将用于纠错的模块用于容错等。当自检模块发现存储颗粒出现故障时,将Mem_state寄存器的相应位置为1。而存储系统的数据组合以及地址生成都是与Mem_state寄存器相关的可配置逻辑。

(1)采用行冗余模块实现容错。当自测逻辑发现某个颗粒出现故障时,首先选择采用行冗余模块进行容错的方法。CS片选信号可以看作地址信号的一部分,当寄存器Mem_state中存在一位为1,则出现故障的颗粒所在的存储颗粒行就会被关闭(拉高CS信号),同时打开冗余行(拉低CS信号),其他信号不变。

(2)将用于纠错的模块用于容错。当自测逻辑发现某个颗粒出现故障且所有的冗余行都已经启用,可以适当将纠错的模块用于容错。这时需要在地址方面和数据重组方面都进行一定的改动,主要包括:①在故障颗粒所在的行内,故障颗粒的地址和数据都被转发到空闲颗粒。②所有的数据线依然直接与控制器模块相连,但在模块内部,数据重组逻辑自动将冗余颗粒的数据通路重组到故障颗粒的数据通路上来。③纠错码编解码逻辑自动调整编解码方案。根据相关寄存器的值,纠错码的编解码逻辑自动降低纠错能力,数据重组逻辑也自动定向纠错码的数据通路。图4为数据重组示意图。

|

|

系统纠错容错能力分析

假设各个DDR颗粒之间发生错误的概率是互相独立的,设每个颗粒发生错误的概率恒定为λ,则每个DDR颗粒的可靠性符合泊松分布,其可靠性为Rm=e-λt。在Mem(i,j)系统中,每行的可靠性为

|

整个系统的可靠性为

重构前后系统可靠性的变化如图5所示。

|

由此,可以根据故障概率λ计算出系统的整体可靠性Rsystem,根据系统要求的可靠性可以反向计算出所需要的i,j,从而构建出完整的Mem(i,j)容错存储系统。

结论

针对SoC实时数字信号处理系统的特点,设计了一种新的具有自适应容错纠错能力的二级冗余存储体系结构。详细论述了系统在存储颗粒组织排列和信号连接方面对于纠错容错能力的支持、系统在逻辑设计上对纠错容错能力的支持等。新的存储系统容错方案可以有效地提高存储系统的可靠性,下一步的工作将集中在整个系统的低功耗优化方面。

上一篇:G.652光缆面面观

下一篇:十法宝确保VoIP协议应用下网络安全