- 易迪拓培训,专注于微波、射频、天线设计工程师的培养

双TSC695F处理器在卫星电子平台中的应用

录入:edatop.com 点击:

容错电路设计

系统容错设计是整个系统设计的关键,容错电路要求简洁、可靠,容错措施包括以下几部分。

1 EDAC容错

利用TSC695F自身的EDAC功能,可以实现内存或总线的EDAC,从而达到对内存和总线的一位或两位错误的纠正和检测。

2 看门狗检测

系统仲裁检测电路中对由双TSC695F组成的主/备用机设置了"看门狗"监视器,系统正常工作时,会周期性地进行"喂狗"动作,当系统发生故障时,"喂狗"动作停止,产生系统复位,如果系统连续四次复位均不正常,则系统仲裁检测电路会进行系统切换操作,切断故障机电源,打开备用机电源。同时,运行故障检测定位程序,找出故障原因。

3 心跳信号检测

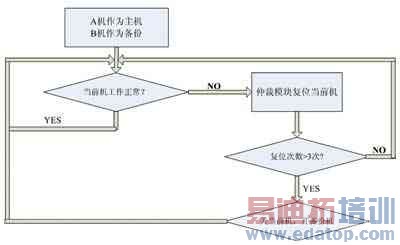

当主机在正常的运行过程当中,会周期性地通过GPIO口发出一系列的方波信号告知系统仲裁模块当前工作正常,当系统故障时,心跳信号消失,由仲裁模块进行复位操作,当5次复位均无效后,进行电源的切换,从而实现容错的目的。

4 双系统自主容错

本系统可以分为冷备用动态双模冗余模式和热备用动态双模冗余模式。

在冷备用动态双模冗余模式下,工作状态如下所述:系统默认A机为主机,B机为备份机,同时关闭B机电源,由两个开关信号GPIO2和GPIO3来控制PLD1和PLD2,PLD1和PLD2的功能主要是实现A/B机总线的开关切换,即选择A机的IO功能总线还是选择B机的IO功能总线,同一时刻只有一路总线有效,默认情况下PLD1工作,PLD2处于热备份状态。当PLD1控制下的IO功能模块出现故障时,产生出错中断,切断PLD1的开关,同时通知CPU切换到PLD2控制下的总线工作,如果PLD2控制下的IO模块也出现了故障,那么这时由FPGA1产生一个信号通知系统仲裁模块关闭A机的电源,打开B机的电源,从而实现双系统间的容错切换。

在热备用动态双模冗余模式下,工作状态如下所述:系统上电后,A机和B机都上电,A机为主模块,B机为从模块,A机B机同步工作,但B机不作系统输出,这样,当进行数据通信时,A机和B机可以对接收的数据进行数据比对。如果发现数据不同,则先由A机进行通道切换,再进行数据的通信,再进行数据比对。如果发现A机出现故障,则系统进行重构:先切除原主模块,再将原备用模块切换为主模块,同时通过读取双口RAM的数据作为最后一次传输的结果,保证数据不丢失。

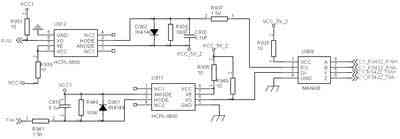

图4 RS422总线接口电路图 |

图5 容错流程图 容错流程如图5如示。 软件开发平台 随着卫星技术的不断发展,以及实际应用需求的不断提高,星务计算机所要处理的任务越来越复杂,其运算量也随之变得越来越大,以往对底层硬件依赖程度较高的"控制流+中断"的程序结构已不能适应星务计算机的发展。为了解决这个问题,我们引入了嵌入式实时多任务操作系统(EOS)——RTEMS,利用珠海欧比特控制工程股份有限公司开发的基于此操作系统的Orbita EOS嵌入式操作系统及其Orbita EOS 开发工具,可大大提高软件编程效率和可靠性,具体可参考Orion4.0用户手册(www.myorbita.net)。 结束语 在采用双TSC695F作为容错星务计算机的研发过程中,笔者深深感觉到容错功能的重要性,容错功能的优良与否直接影响到星务计算机在轨的生存能力,除了硬件上的容错外,软件方面的容错也不容忽视。

上一篇:浅谈Oracle中的三种Join方法

|