- 易迪拓培训,专注于微波、射频、天线设计工程师的培养

基于FPGA的DES、3DES硬件加密技术

录入:edatop.com 点击:

传统的加密工作是通过在主机上运行加密软件实现的。这种方法除占用主机资源外,运算速度较慢,安全性也较差。而硬件加密是通过专用加密芯片、FPGA芯片或独立的处理芯片等实现密码运算。相对于软件加密,硬件加密具有加密速度快、占用计算机资源少、安全性高等优点。

设计思路

本设计首先用硬件描述语言(VHDL)进行DES(数据加密标准)、3DES(三重DES)算法编码和系统设计,然后采用FPGA来具体实现。采用FPGA设计灵活,可对芯片内部单元进行配置,可以缩短设计周期和开发时间,同时经过优化可以达到较高的性能。另外有多种EDA开发软件支持FPGA的设计,在本设计中采用了EDA综合工具Synplify和Altera公司的Quartus II 7.2开发软件。

系统的硬件结构

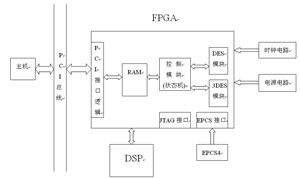

整个系统由FPGA、DSP、时钟电路、电源电路等部分组成,如图1所示。FPGA是系统的核心器件。DSP作为控制单元,控制数据的传输。系统的工作过程是这样的:在DSP的控制下,主机中待加密的明文数据通过PCI总线传送到FPGA的RAM区,然后启动控制模块的状态机,把明文送入DES模块或3DES模块进行相应的加密运算。运算的结果(密文)再返回到主机中。FPGA自带的JTAG接口用来连接下载电缆到主机的并口,便于用逻辑分析议对系统调试。EPCS4是FPGA的配置芯片,用来存储程序。由于系统掉电后FPGA内的程序将丢失,所以每次上电后FPGA首先从EPCS4里读取相应的配置信息。

设计思路

本设计首先用硬件描述语言(VHDL)进行DES(数据加密标准)、3DES(三重DES)算法编码和系统设计,然后采用FPGA来具体实现。采用FPGA设计灵活,可对芯片内部单元进行配置,可以缩短设计周期和开发时间,同时经过优化可以达到较高的性能。另外有多种EDA开发软件支持FPGA的设计,在本设计中采用了EDA综合工具Synplify和Altera公司的Quartus II 7.2开发软件。

系统的硬件结构

整个系统由FPGA、DSP、时钟电路、电源电路等部分组成,如图1所示。FPGA是系统的核心器件。DSP作为控制单元,控制数据的传输。系统的工作过程是这样的:在DSP的控制下,主机中待加密的明文数据通过PCI总线传送到FPGA的RAM区,然后启动控制模块的状态机,把明文送入DES模块或3DES模块进行相应的加密运算。运算的结果(密文)再返回到主机中。FPGA自带的JTAG接口用来连接下载电缆到主机的并口,便于用逻辑分析议对系统调试。EPCS4是FPGA的配置芯片,用来存储程序。由于系统掉电后FPGA内的程序将丢失,所以每次上电后FPGA首先从EPCS4里读取相应的配置信息。

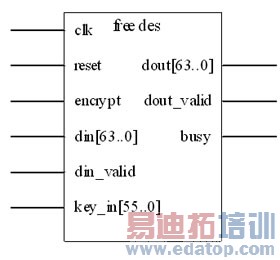

图1 系统结构框图 考虑到本设计中FPGA的RAM容量不能太小,以便存储较多的数据;另外用户I/O引脚数量应有一定的富裕。最终选择了Altera公司Cyclone III系列的EP3C25F256C8。其I/O引脚数是156个,RAM总量为608Kb。 3DES模块的设计 采用VHDL编程实现DES算法后,通过Synplify生成一个基本的模块——DES核(如图2所示)。

|