- 易迪拓培训,专注于微波、射频、天线设计工程师的培养

DDR2 SDRAM介绍及其基于MPC8548 CPU的硬件设计

录入:edatop.com 点击:

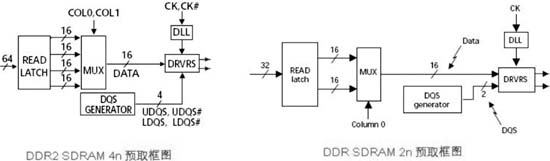

* 4n数据预取

DDR SDRAM的数据预取能力是2,即芯片内部能以2倍于时钟运行的速度预取数据,从而使得芯片内核工作频率仅需要为外部数据传输率的一半。DDR2 SDRAM的数据预取能力是4,即芯片内核工作频率仅需要为外部数据传输率的1/4。而对于SDRAM,芯片内核工作频率等于外部数据传输速率。所以在同样的内核频率下,DDR SDRAM的数据传输速率比SDRAM高一倍,而DDR2 SDRAM的数据传输率比DDR SDRAM又高一倍。

例如,DDR2和DDR1 SDRAM的外部数据传输率都为400Mb/s的情况下,对于DDR2 SDRAM而言,其内核工作频率仅需要为100MHz,而对于DDR SDRAM,其内核工作频率需要为200MHz,如果是SDRAM,则其内核频率要求为400MHz,正是因为如此高的内核频率无法在技术上实现,因而SDRAM的数据传输率无法达到400Mb/s。

利用这项技术,DDR2 SDRAM可以在不提高内核工作频率的前提下(即无需对芯片做大的技术革新),大大提高外部数据传输速率,从而获得更高的性能。值得提及的是,目前正在研发的DDR3 SDRAM技术,其数据传输率比DDR2 SDRAM又有大幅度提高,其并不是源于技术上的巨大变革,而是因为采用了8n数据预取技术。

根据数据传输速率的不同,DDR SDRAM有如下系列:266Mb/s,333Mb/s, 400Mb/s,而DDR2 SDRAM有如下系列:400Mb/s,533Mb/s, 667Mb/s,800Mb/s, 1066Mb/s。可以看出,DDR2 SDRAM直接从DDR SDRAM的最高的数据传输率起步,最高可以达到1066Mb/s以上,该性能的大幅提升,正是利用了这种4倍数据预取技术。

图5提供了DDR SDRAM和DDR2 SDRAM的数据预取框图以便比较。

DDR SDRAM的数据预取能力是2,即芯片内部能以2倍于时钟运行的速度预取数据,从而使得芯片内核工作频率仅需要为外部数据传输率的一半。DDR2 SDRAM的数据预取能力是4,即芯片内核工作频率仅需要为外部数据传输率的1/4。而对于SDRAM,芯片内核工作频率等于外部数据传输速率。所以在同样的内核频率下,DDR SDRAM的数据传输速率比SDRAM高一倍,而DDR2 SDRAM的数据传输率比DDR SDRAM又高一倍。

例如,DDR2和DDR1 SDRAM的外部数据传输率都为400Mb/s的情况下,对于DDR2 SDRAM而言,其内核工作频率仅需要为100MHz,而对于DDR SDRAM,其内核工作频率需要为200MHz,如果是SDRAM,则其内核频率要求为400MHz,正是因为如此高的内核频率无法在技术上实现,因而SDRAM的数据传输率无法达到400Mb/s。

利用这项技术,DDR2 SDRAM可以在不提高内核工作频率的前提下(即无需对芯片做大的技术革新),大大提高外部数据传输速率,从而获得更高的性能。值得提及的是,目前正在研发的DDR3 SDRAM技术,其数据传输率比DDR2 SDRAM又有大幅度提高,其并不是源于技术上的巨大变革,而是因为采用了8n数据预取技术。

根据数据传输速率的不同,DDR SDRAM有如下系列:266Mb/s,333Mb/s, 400Mb/s,而DDR2 SDRAM有如下系列:400Mb/s,533Mb/s, 667Mb/s,800Mb/s, 1066Mb/s。可以看出,DDR2 SDRAM直接从DDR SDRAM的最高的数据传输率起步,最高可以达到1066Mb/s以上,该性能的大幅提升,正是利用了这种4倍数据预取技术。

图5提供了DDR SDRAM和DDR2 SDRAM的数据预取框图以便比较。

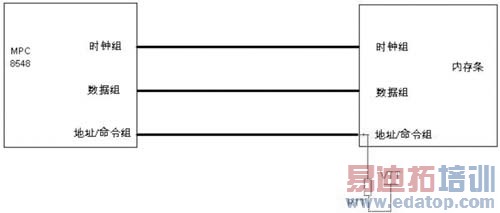

图5 16位存储芯片的数据预取框图 * 差分DQS/DQS#信号 DDR SDRAM采用单端DQS信号。 如前文所述,目前广泛应用的DDR2 SDRAM,数据传输率最高已经达到1066Mbit/s,即DQS和DQ的变化率都将达到一秒钟1066M次,其中,DQS作为数据信号DQ的采样参考源,如果采用单端信号已经不足以保证其在高速变化时的信号完整性。 采用差分DQS/DQS#信号,其优势在于:减少信号间串扰的影响,减少DQS输出脉宽对工作电压和温度稳定性的依赖等。因而,建议在使用数据传输率为533Mb/s以上的DDR2 SDRAM系列时,尽量采用差分DQS/DQS#信号。 使能差分DQS信号是通过设置DDR2 SDRAM的EMR寄存器的第10位为0来实现。 * 功耗和封装 DDR SDRAM的电平常用SSTL-2,即信号引脚是利用2.5V电源供电,而DDR2 SDRAM则采用SSTL-18电平,即信号引脚是利用1.8V电源供电。在相同存储容量和相同数据传输率的情况下,DDR2 SDRAM将有更低的功耗。 DDR SDRAM的封装种类有:66引脚的TSOP封装,60引脚的FBGA封装。由于DDR SDRAM的数据传输率不是特别高,因此TSOP封装能较好的工作在这种频率上。而DDR2 SDRAM的最高数据传输率已经达到1066Mb/s,在高频下,TSOP封装的过长的引脚将产生很高的感抗和寄生电容,严重影响芯片工作的稳定性。 DDR2 SDRAM直接采用FBGA封装,基于其良好的电气性能和散热性,保证了芯片在高速工作下的稳定性。 由于DDR2 SDRAM有4位,8位,16位(芯片的DQ引脚的数目,16位表示芯片有16根DQ引脚)三种不同系列,因而无法采用统一引脚数目的封装。目前,4位和8位的芯片采用60或者68引脚的FBGA封装,16位的芯片采用92或者84引脚的FBGA封装。 * OCD OCD(Off-Chip Driver)即离线驱动调整技术。这是DDR2 SDRAM刚问世时开发的技术,而目前的DDR2 SDRAM芯片已不再支持该技术【2】,因此不再详述。 基于MPC8548 CPU的应用 MPC8548是Freescale公司开发的新一代PowerQUICC III系列的高性能处理器。其内部工作频率可达1.33GHz,在该工作频率上处理性能可达3065 MIPS。一级缓存有指令缓存和数据缓存各32KB,二级缓存为512KB,支持DDR1和DDR2存储器控制器,支持PCI,PCI-X和PCI Express接口,支持SRapid IO接口,支持4个GbE接口。本文将重点讨论基于MPC8548的DDR2 SDRAM接口的硬件设计。 MPC8548最高支持667Mb/s数据传输率的DDR2 SDRAM。因此选型中需要注意不能选用800Mb/s和1066Mb/s系列的芯片。本设计中选用667Mb/s数据传输率的DDR2 SDRAM的DIMM(Dual-Inline-Menory-Modules,双列内存条)内存条,每个内存条上包含9片8位的DDR2 SDRAM 芯片,组成64位数据线和8位ECC(Error Checking and Correcting,错误检查和纠正)校验线的工作方式。 DDR2 SDRAM接口的信号线分为4组,以下以MPC8548命名方式为准,命名和DDR2 SDRAM芯片资料的区别在于信号名之前多一个字母"M"【7】: 1) 数据组:MDQS/MDQS#[8:0], MDM[8:0], MDQ[63:0], MECC[7:0] 2) 地址组:MBA[2:0], MA[15:0], MRAS#, MCAS#, MWE# 3) 命令组:MCS#[3:0], MCKE[3:0], MODT[3:0] 4) 时钟组:MCK/MCK#[5:0] PCB设计时,建议布线顺序依次为:数据组,地址组,控制组,时钟组,电源。 对于单端信号线,阻抗控制在50~60欧姆内。对于差分信号线,阻抗控制在100~120欧姆内。 如果使能了ODT功能,数据组无需外部匹配电阻,走线直接从MPC8548连接到内存条即可。而地址组和命令组需要在内存条末端利用外部电阻RTT上拉到VTT电平实现匹配,电阻值需要经过仿真确定。如图6,考虑到最佳的信号完整性,RTT应该放在内存条之后,即地址/命令组信号走线从MPC8548出来,应该先到内存条的引脚,然后再走到RTT电源平面实现终端匹配。对于时钟组,一般而言,内存条上都包含了100~120欧姆的差分终端电阻,所以在PCB上无需外加匹配。

|