- 易迪拓培训,专注于微波、射频、天线设计工程师的培养

DDR2 SDRAM介绍及其基于MPC8548 CPU的硬件设计

录入:edatop.com 点击:

DR2(Double Data Rate 2,两倍数据速率,版本2) SDRAM,是由JEDEC标准组织开发的基于DDR SDRAM的升级存储技术。 相对于DDR SDRAM,虽然其仍然保持了一个时钟周期完成两次数据传输的特性,但DDR2 SDRAM在数据传输率、延时、功耗等方面都有了显著提高,而这些性能的提高,主要来源于以下技术的提升:ODT,Post CAS,4n数据预取,封装等。

* ODT

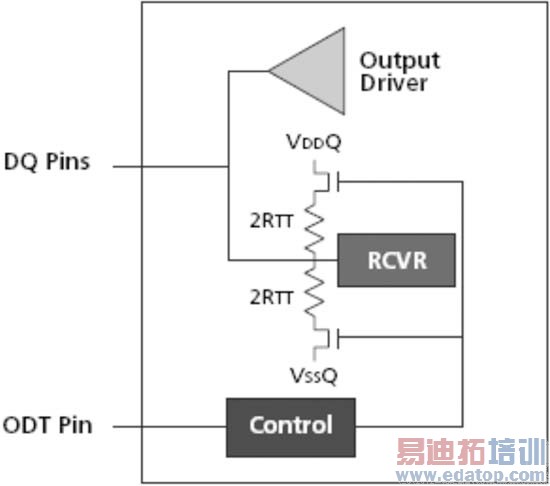

ODT(On-Die Termination),即芯片内部匹配终结。

在DDR SDRAM应用中,需要通过大量的外部电阻上拉到VTT电平(1.25V)以实现信号匹配,以16位芯片为例,以下信号需要通过这种方式进行匹配:

CK,CK#,DQ[15:0],LDQS,UDQS, ADDR[10:0],RAS#,CAS#,WE#,即一片芯片需要34个外部上拉电阻,极大的占用了宝贵的PCB面积。同时,由于DQ[15:0],LDQS,UDQS等信号是双向信号,即读和写时,对匹配电阻的位置有不同要求,因此在电阻布局时很难在两个方向上同时实现最佳的信号完整性。

在DDR2 SDRAM中,采用ODT技术将许多外部的匹配电阻移到芯片内部从而节省了大量的PCB板上面积。另外,ODT技术允许存储控制器(如下文的MPC8548 CPU)通过配置DDR2 SDRAM的内部寄存器以及控制ODT信号,来实现对匹配电阻的值及其开关状态进行控制,从而可以实现读,写操作时最佳的信号完整性。

* ODT

ODT(On-Die Termination),即芯片内部匹配终结。

在DDR SDRAM应用中,需要通过大量的外部电阻上拉到VTT电平(1.25V)以实现信号匹配,以16位芯片为例,以下信号需要通过这种方式进行匹配:

CK,CK#,DQ[15:0],LDQS,UDQS, ADDR[10:0],RAS#,CAS#,WE#,即一片芯片需要34个外部上拉电阻,极大的占用了宝贵的PCB面积。同时,由于DQ[15:0],LDQS,UDQS等信号是双向信号,即读和写时,对匹配电阻的位置有不同要求,因此在电阻布局时很难在两个方向上同时实现最佳的信号完整性。

在DDR2 SDRAM中,采用ODT技术将许多外部的匹配电阻移到芯片内部从而节省了大量的PCB板上面积。另外,ODT技术允许存储控制器(如下文的MPC8548 CPU)通过配置DDR2 SDRAM的内部寄存器以及控制ODT信号,来实现对匹配电阻的值及其开关状态进行控制,从而可以实现读,写操作时最佳的信号完整性。

图1 ODT功能图 DDR2 SDRAM芯片提供一个ODT引脚来控制开或关芯片内部的终结电阻。在只有一个DDR2 SDRAM芯片作为存储器控制器的负载的情况下,写操作时,由于DDR2 SDRAM作为接收端,所以ODT引脚为高电平以打开芯片内部终结电阻;读操作时,由于DDR2 SDRAM作为发送端,所以ODT引脚为低电平以关闭芯片内部终结电阻。其中,ODT引脚的状态由存储器控制器(如MPC8548)来控制。 ODT终端电阻值RTT可以通过DDR2 SDRAM内部的EMR寄存器来设定:首先配置EMR[15:14]=01来选定该寄存器工作于EMR(扩展模式寄存器)模式,然后通过EMR[6]和EMR[2]两位来设置内部RTT的值,允许选择为RTT关闭,75欧姆,150欧姆,50欧姆这四种模式。以选择75欧姆这种模式为例,图1中,DQ引脚内部的上拉电阻和下拉电阻将配置为150欧姆。 需要注意,DDR2 SDRAM的ODT技术,只是对DQ,DQS,DM这些信号(在选择了差分DQS的情况下,也包括DQS#信号)实现了内部匹配。而地址和控制信号等仍需要通过外部匹配。 * Posted CAS 以读DDR2 SDRAM为例。

|