- 易迪拓培训,专注于微波、射频、天线设计工程师的培养

串行取代并列技术的后DDR2世代发展

半导体材料制作的内存分为以DRAM为主的挥发性(Volatile)内存,加上非挥发性(Non-Volatile)内存的NAND Flash、NOR Flash,即占有目前内存市场的90%以上。两者都在寻觅后续之次世代继承产品,发展态势很明显,由于共通性的考虑,都以非挥发性内存的研究为主,大致上形成磁阻内存(MRAM)、铁电内存(FeRAM)与相变化内存(PCM)竞逐的情况。

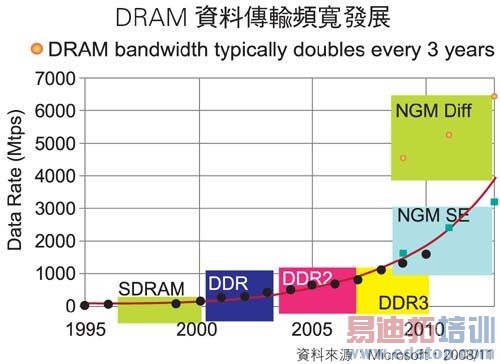

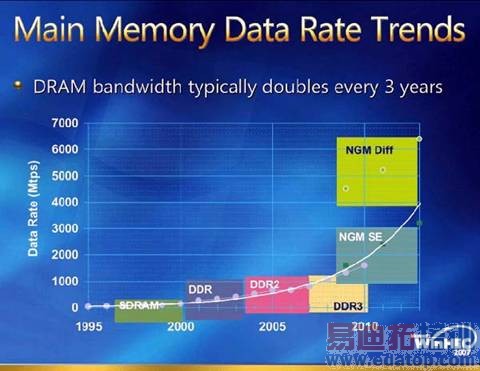

图说:由于成本与专利等问题,次世代非挥发性内存取代现有内存,特别是挥发性内存,恐怕还有相当的难度,现有的DRAM实际上也历经了相当多次的世代交替,目前刚刚到位的DDR3内存与JEDEC已经发布的DDR4,加上显示内存GDDR5的技术发展,也不可轻忽。

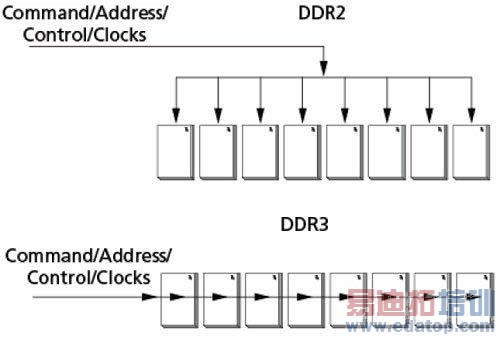

DRAM技术正由DDR2过渡到DDR3中,虽名称看似有承传的概念,但实际DDR3内存技术已较前一代DDR2架构大大不同!设计上作了相当多的改变,尤其是传输拓朴方面的更新,更类似DDR频率上/下缘都可传输讯号,这也是DDR胜过SDRAM性能的最大转变。

观察自SDRAM以来,都是采顶点并联式传输拓朴,因传输迟延(latency)较低,否则,多颗颗粒间的讯号传输与迟延,极可能产生不一致问题!因限于制程与技术瓶颈,大容量DRAM多是由多颗颗粒并联而成。但容量有了,数据无法避免传输量方面问题,也必须想办法解决,特别是中央处理器运作速度不断攀升,内存也必须能提供更快的运算数据。

提高DRAM速率的方式则是利用更大位宽与更高频率,提高位宽的方式较为困难,因为线路设计会随着位宽加大而增加复杂度,内存PCB与主机板PCB都有执行上的困难(或成本过高问题),最后则发展出双信道甚至3信道技术,不过一样占用大量主机板PCB空间。

DDR3架构彻底更新 串联架构取代并联设计

由于提高位宽难度相当高,因此内存走向提高同一频率传输数据量的技术,让DDR取代SDRAM,甚至RDRAM成为主流架构,但是内存由于PCB板电气讯号限制而无法实行QDR技术,所以,DDR也必须提高频率,增加传输数据效率,JEDEC(Joint Electronic Device Engineering Council)组织亦不断提出更高速的内存规范。

不过直到DDR2-800之后,并联式传输架构频率提升遭遇瓶颈,因同级路线各分支数据分流会随着频率提高,噪声也会同时增加,很容易产生分流数据错误的严重问题,而大部分DRAM为了压低成本,多半未设置ECC(Error-Correcting Code)机制,让这个问题愈来愈严重,因此,DDR2也很难藉由拉高频率提高效能。

当DDR3传输拓朴改为串联架构,即序列化运作模式(称为Fly-by拓朴),利用共同控制讯号线连结所有颗粒组(目前以2颗为1组),如同所有串行传输架构更容易提高频率,因为序列运作1线控制到底,包括频率、寻址、命令以1条路线完成,用以控制路线上的各组内存芯片。

此外,串行传输比并列架构更省电,因为并列为让高频率下每1个颗粒都有正确讯号,电压也必须加大,但是DDR3并列传输则将电压分开,控制路线采VREFCA电压、控制内存数据总线使用VREFDQ电压,因而电压能降得更低,DDR2标准电压约1.8v,但目前最新规范的DDR3低电压版已降到1.35v。

DDR3尚未接班完整 次世代DDR4技术已出现

DDR3架构虽可创造高频率、低电压…等优点,但却也创造出新缺点,即利用串行传输拓朴,第1组内存与最后1组内存接收讯号与动作时间必定会有微小落差,因此产生迁移时间偏差(Flight Time skew),内存控制器必须有写入/读取的校准机制(Write/Read Leveling),但也会产生额外迟延,所以同频率下DDR3效率会低于DDR2。

DDR3迟延限制可由高频率弥补,与DDR2相对于DDR的情况类似,不过改良技术已经推出,即JEDEC公布的DDR4规格,将根基于DDR3基础,更进一步加强效率,目前最高规格DDR3-1600数据频率为1.6GHz,每信号脚位为1.8Gbps传输率,而DDR4将达到3.2GHz(可能命名为DDR4-3200),每信号脚位提供3.2Gbps传输能力。

DDR系统中不断提升的信号预取机制,DDR4也会提高为DDR3的2倍(即达到16bit),内建终端动态电阻与内存模块为64位宽…等特性不变。不过在信号传输机制上,DDR4却出现2种方案:其一是传统SE单点讯号模式(Single-ended Signaling)单点信号,另1个方案则是差分讯号技术(Differential Signaling)。

传统SE讯号架构优点在于所需路线较少,PCB布线工作相对容易,但讯号频率不断提高的现况下,即便采串行架构也会产生严重干扰!差分讯号技术则利用1条线路来传送1个讯号,透过电压差再决定讯号数值,具很强的抗干扰能力,而此理论模型当摆到DDR4设计实务中,采SE讯号的DDR4则可提供前述的3.2Gbps传输能力,但是差分讯号版本将可提供多一倍(6.4Gbps)的传输实力。

DDR4预计将上看频率超过2GHz(2,133MHz),不过前述2种版本的DDR4内存并不兼容,或许将使DDR4阵营分裂,而为了整体发展考虑,JEDEC倾向以SE讯号版的DDR4取代DDR3,预计2009年推出样品,并在2010年或2011年商品化取代DDR3,但是差分讯号版DDR4将更晚推出,作为更新世代的未来架构。

图说:挥发性内存阵营技术表现,主要由传输频宽不断提高显现。(Microsoft)

|