● 读写数据的设计

在设计好采集数据的地址发生单元后,接下来就是配合时序进行读写操作。

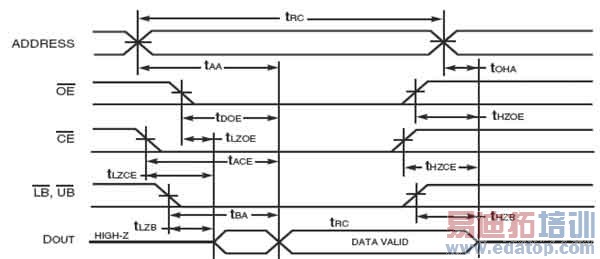

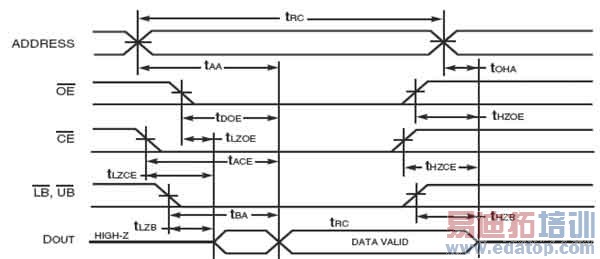

图4是RAM的读操作时序图,从图中可以看出,当指定待操作的地址后,设置芯片使能信号OE和片选使能信号CE有效,即可从数据线上读出相应地址内的数据。

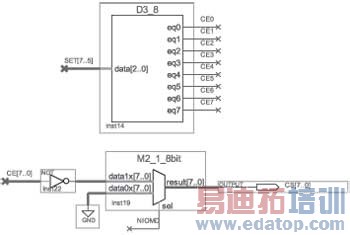

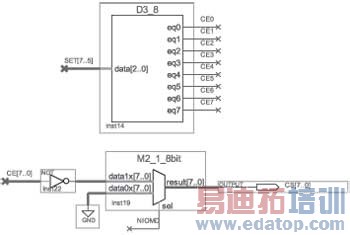

图4 RAM的读数据时序图 对于单片RAM的操作比较简单,但是要将数据顺序写入8片RAM中,就要求对上一片RAM写操作完成后,系统能够设置下一个待操作的RAM 有效,128位数据线分别对应8片RAM的数据线,由于地址线和读写使能线公用,则需要分别设置每个RAM的片选,以区别当前操作是针对哪一个RAM。片 选信号可以由译码器产生。读操作时设置相应RAM的片选有效,即可读出存储的数据,而进行写操作时,则可以设置所有的RAM片选有效,将采集到的数据同时 并行的写入8片RAM中。根据这些描述,片选信号的设计如图5所示。NIOMD为操作的状态信号,说明当前的操作是读状态或是写状态,读数据情况下设置为 1,片选信号分别有效,写数据情况下设置为0,所有RAM均处于片选有效状态下,可以同时写入数据。这样的设计也是为了配合系统的需求,一般的,读取数据 的速度相对于写数据来说还是要快一些的。

图5 RAM片选使能信号设计 仿真验证

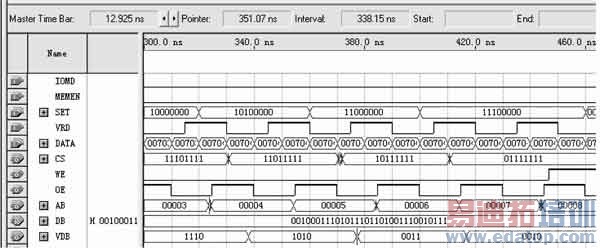

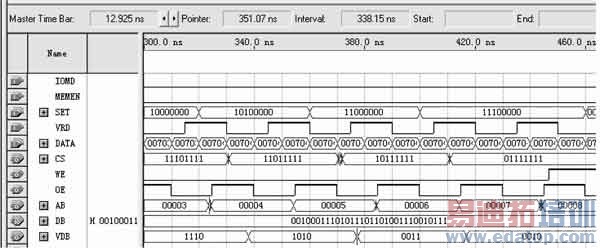

将上述设计方案整合后,配合其他控制信号的设计,就完成了数据采集系统数据存储功能的设计。在QuartusII软件中对上述设计进行波形 仿真,可以看到设置SET值及相应的状态控制信号,则在VDB端就可以按照CS指示的相应的RAM芯片中顺序读出预先存入的数据。按照图中所示的状态寄存 器设置,读取深度设置寄存器设置为最小值SET[4...1]=000,即只读每片RAM的首个存储数据,则地址发生器的最高值为8,从图中可以看到当地 址发生器输出值增加到8时,WE跳变为高电平,RAM的读使能无效。由于AB[3]=1,使得CNTEN=1,地址发生器的计数时钟使能无效,计数器停止 计数,完成一轮数据的读取操作。读数据仿真验证结果如图6所示。

图6 读数据仿真验证 在图6中,对于当前数据线上的数据串DB=0010,0011,1010,1110,1101,0011,1001,0111,片选信号 CS低电平有效,当CS=11011111时,即选中按顺序由低位到高位计算的第6片RAM,此时对应的在VDB上读出的数据应该为DB的第6个数据值, 即为1010。从波形方针图上得到验证。

结语

利用FPGA的内部资源,设计灵活的逻辑控制,完成高速大容量数据采集的存储和传输设计,本文提出的设计方案可以在选用低成本、操作简单的 静态RAM组的情况下,实现实时大容量数据存储需求的一种设计方法,并在EDA软件中进行了仿真验证,成功地应用在1GS/s数据采集模块中。

上一篇:硬盘部分常见故障汇总

下一篇:国内最快HPC背后悬疑获解

国内最全面、系统、专业的手机天线设计培训课程,没有之一;是您学习手机天线设计的最佳选择...【More..】

国内最全面、系统、专业的手机天线设计培训课程,没有之一;是您学习手机天线设计的最佳选择...【More..】

射频工程师养成培训课程套装,专家授课,让您快速成为一名优秀的射频工程师【More..】

射频工程师养成培训课程套装,专家授课,让您快速成为一名优秀的射频工程师【More..】

网站地图

| | |