- 易迪拓培训,专注于微波、射频、天线设计工程师的培养

基于ARM9内核Processor对外部NAND FLASH的控制实现

1 NAND FLASH

NAND写回速度快、芯片面积小,特别是大容量使其优势明显。页是NAND中的基本存贮单元,一页一般为512 B(也有2 kB每页的large page NAND FLASH),多个页面组成块。不同存储器内的块内页面数不尽相同,通常以16页或32页比较常见。块容量计算公式比较简单,就是页面容量与块内页面数的乘积。根据FLASH Memory容量大小,不同存储器中的块、页大小可能不同,块内页面数也不同。例如:8 MB存储器,页大小常为512 B、块大小为8 kB,块内页面数为16。而2 MB的存储器的页大小为256 B、块大小为4 kB,块内页面数也是16。NAND存储器由多个块串行排列组成。实际上,NAND型的FLASHMemory可认为是顺序读取的设备,他仅用8 b的I/O端口就可以存取按页为单位的数据。NAND在读和擦写文件、特别是连续的大文件时,速度相当快。

2 NAND FLASH与NOR FLASH比较

NOR的特点是可在芯片内执行,这样程序应该可以直接在FLASH内存内运行,不必再把代码读到系统RAM中。NOR的传输效率很高,但写入和读出速度较低。而NAND结构能提供极高的单元密度,并且写入和擦除的速度也很快,是高数据存储密度的最佳选择。

这两种结构性能上的异同主要为:NOR的读速度比NAND快;NAND的写入速度比NOR快很多;NAND的擦除速度远比NOR快;NAND的擦除单元更小,相应的擦除电路也更加简单;NAND的实际应用方式要比NOR复杂得多;NOR可以直接使用,并在上面直接运行代码,而NAND需要I/O接口,因此使用时需要驱动程序。

3 NAND FLASH在系统中的控制

在没有NAND FLASH硬件接口的环境中,通过软体控制CPU时序和硬件特殊接线方式实现仿真NANDFLASH接口,进而实现在嵌入式系统中脱离NANDFLASH专用硬件接口进行对NAND FLASH读、写、擦除等操作的实现方法。

本方法主要工作在以下两个方面:

软件方面:针对特殊硬件线路的软体设计和严格的CPU时序控制;

硬件方面:硬件的线路设计,利用NOR FLASH专用硬件接口控制NAND FLASH。

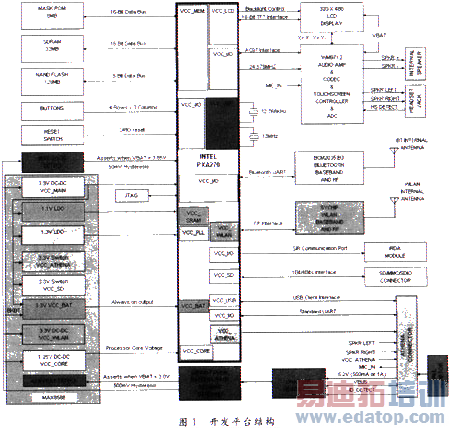

首先建立的开发平台如图1所示。

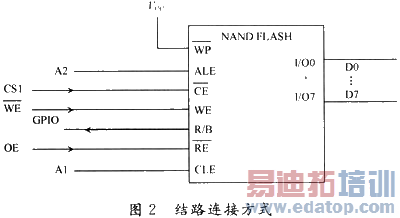

本平台使用Intel的PXA270 Processor,无内建NAND FLASH Controller,使用NOR FLASH Controller控制NAND FLASH,具体的线路连接方式如图2所示。

上一篇:Zed-3推出VoIP城市应急指挥调度应用方案

下一篇:光网络的动态特性与可扩展性