- 易迪拓培训,专注于微波、射频、天线设计工程师的培养

四通道I2C多路复用器提供了地址扩展、总线缓冲和故障管理

录入:edatop.com 点击:

引言

随着数据处理、海量存储和通信系统的发展,用于传送诸如温度、扇速、系统电压和关键产品数据(VPD,例如:电路板标识)等信息的子系统尺寸和复杂程度成比例地增长。在这些信息的传送中,最常用的就是两线式串行总线,比如:I2C或SMBus。

在这些系统的设计中会出现若干实际问题,特别在系统规模日益扩大的情况下更是如此。首先,诸如小型可插拔式光学模块(SFP)等众多设备都具有硬连线I2C地址,故由于地址冲突的原因而无法使用多个这样的设备。其次,由于设备种类的增加以及有越来越多的I/O板卡需要在系统上进行热插拔,因此,I2C设备产生混乱并把总线保持于低电平的可能性有所增加。第三,随着等效总线电容的增加,总线定时规格的满足变得困难起来。除了这些大的系统问题之外,在安装一个新的I/O板卡时进行功率循环并不是任何规格的不间断电源都拥有的功能选项。

具有总线缓冲器的LTC4306四通道两线式总线多路复用器/开关解决了所有这些问题。上行两线式总线(SDAIN、SCLIN)上的一个主控器可通过LTC4306的总线缓冲器和多路复用器/开关连接至下行总线的任何组合。因此,相同的设备地址可在多根下行总线上使用。缓冲器在上行和下行总线之间提供了容性隔离,从而为系统负载的分割创造了条件。上升时间加速器在克服电容局限性方面起到了进一步的帮助作用。当总线处于低电平的持续时间达到了设定的长度时,阻塞低电平超时电路将使上行总线与下行总线断接,从而把上行总线解放出来,以恢复通信。最后,LTC4306的任何两线式总线引脚都可在一个带电系统上进行插拔操作,而不会对其造成损害。LTC4306可采用2.7V至5.5V的电源电压。

一般操作

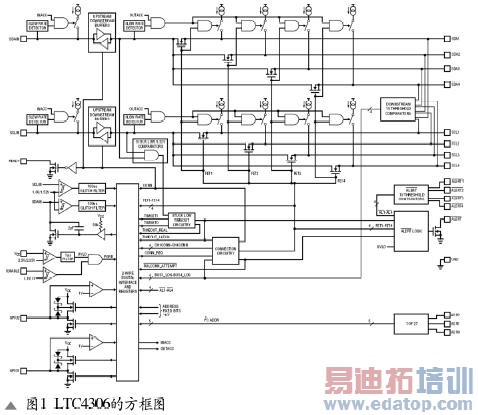

图1示出了LTC4306的方框图。UVLO比较器将阻止LTC4306接收命令,直到VCC电压升至2.5V(典型值)以上为止。这将确保LTC4306在其拥有足够的偏置电压之前不会试图运行。当ENABLE引脚被拉至1V以下时,LTC4306将被复位至其缺省的高阻抗状态,并且毫不理会在其两线式总线上进行的任何通信尝试。当ENABLE引脚被回拉至1.1V以上时,主控器可以恢复与LTC4306的通信。

与一根阻塞总线断接

当两线式总线阻塞于低电平的持续时间达到了一个设定的长度时,LTC4306将使上行总线与下行总线断接。主控器随后处于空闲状态,以在上行总线上恢复通信(假定问题的起因存在于一根下行总线上)。阻塞低电平超时电路负责监视下行SDA和SCL开关的两个共用的内部节点,并在任一个内部节点电压低于0.52V的情况下运行一个定时器。当这两个内部电压均高于0.6V时,该定时器将被复位。利用寄存器2,主控器能够设定7.5ms、15ms或30ms的时间,或者,它们也可选择停用超时功能。

两线式总线缓冲器和多路复用器开关提供了电容缓冲和电平移动

主控器向寄存器3写入数据,以连接至下行通道的任何组合。两线式总线缓冲器在上行SDAIN、SCLIN总线和下行总线之间提供容性隔离。由于拥有了此项功能,主控器便可在其系统的不同位置上采用LTC4306,以把一根大型总线分裂成若干个较小的总线。当连接了任何下行总线时,LTC4306将允许通过一个外部电阻器把READY引脚拉至一个逻辑高电平。

按照缺省设置,LTC4306仅与高电平的下行总线相连。与低电平下行总线相连的尝试将是劳而无功的,并将导致LTC4306把ALERT#引脚拉至低电平,以表示发生了一个故障。主控器可通过向寄存器2写入数据并指示LTC4306执行连接命令(这与下行总线的逻辑状态无关)来取代该功能。

上行和下行总线上拉电源电压可在2.2V至5.5V的范围内变化,而不受LTC4306 VCC电压的影响—— LTC4306因而能够在具有不同上拉电压的总线之间提供电平移动。为了保证同时连接多个下行通道时的正确运作,需确定LTC4306 VCC电压低于或等于所有的下行上拉电压,以维持逻辑高电平期间的通道至通道隔离度。

上升时间加速器缩短了上升时间

通过向寄存器2写入数据,主控器便可以起动或不起动上行总线和下行总线上的上升时间加速器。当起动时,加速器以一种受控方式接通,并向总线输送电流,以使它们在正总线转换期间以一个100V/μs的典型速率上升。这些大上拉电流使得用户能够在仍旧满足上升时间规格的同时构建庞大的重容性系统,但也进行了转换限制,以驱动长电缆。此外,由于加速器提供了强驱动,系统设计师因而能够选择大上拉电阻器来最大限度地减小总线逻辑低电压,由此实现逻辑低噪声容限的最小化。

故障信息为诊断提供了帮助

在发生了一个故障且LTC4306把ALERT#引脚拉至低电平之后,LTC4306将和主控器一道工作,以简单而迅速地解决故障。LTC4306把特定的故障信息存储于只读寄存器0之中。被存储的故障包括低电平阻塞总线、下行总线上的故障以及与一个下行通道的失败连接尝试。

如果故障的起因存在一根连接下行总线之上,则主控器可直接与出错器件进行通信。在这种场合,LTC4306以透明的方式运作,且主控器和出错器件通过LTC4306的总线缓冲器直接通信。

在所有其他的场合中,LTC4306与上行两线式总线上的主控器进行通信,以解决故障。在主控器发送了报警响应地址(ARA)之后,LTC4306利用其位于SDAIN上的地址做出响应,并释放ALERT#。如果由主控器来对其进行寻址,则LTC4306也将释放ALERT#。主控器通过读出寄存器0的内容来确定故障的起因。在主控器解决了问题之后,它把一个空字节写入寄存器0(这是一个只读寄存器),以使故障检测电路复位。

嵌套寻址和电平移动

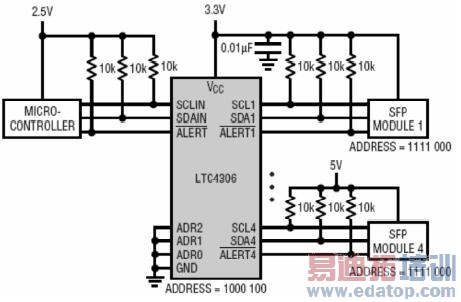

图2所示电路示出了LTC4306的嵌套寻址、电平移动和电容缓冲功能。为简单起见,图中仅给出了通道1和4。请注意,背板、板卡1和板卡4被上拉至三个不同的电源电压。另外,虽然SFP模块具有相同的地址,但是,只要通道1和4决不同时运行,就不会发生地址冲突。

LTC4306位于背板之上时的两线式总线热插拔

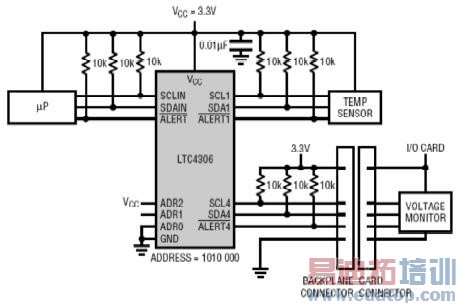

图3示出了一个把LTC4306布设于背板之上并将一个I/O板卡插入下行通道4之中的电路。同样,为简单起见略去了通道2和3。在进行板卡插拔操作之前,需确定通道4未与上行总线相连,这样上行总线上发生的任何事务处理都不会受到干扰。如图所示,SDA4和SCL4上的上拉电阻器位于背板上,不过它们也可以安放在I/O板卡上,只要背板上的主控器在没有板卡插入时不与通道4相连即可。ALERT4#上的上拉电阻器必须设置在背板上,以防止在未插入板卡时发生错误的故障报告。

LTC4306位于I/O板卡之上时的两线式总线热插拔

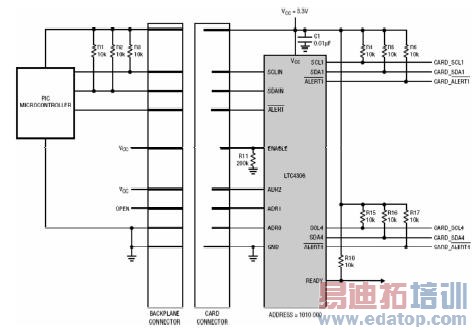

在图4中,LTC4306位于具有4根单独下行总线的I/O板卡的边缘。把一个200kΩ电阻器从ENABLE引脚连接至地,并使ENABLE成为连接器上最短的引脚。这将确保ENABLE引脚在所有其他引脚均连接的情况下保持在一个恒定的逻辑低电平,因此,LTC4306将处于其缺省的高阻抗状态,且不会受到在连接期间SDAIN和SCLIN上连接瞬变的影响。此外,应使ALERT# 连接器引脚比VCC引脚短,这样,VCC就将在ALERT# 形成连接之前建立起与I/O板卡上拉电源引脚的可靠连接,并向ALERT1# ~ ALERT4#上的上拉电阻器供电。当断接时,ENABLE首先断开连接,并使LTC4306复位至其缺省状态,因而当板卡断接时其在SDAIN和SCLIN总线上引起的扰动极小。

结语

LTC4306使得与大型两线式总线系统相关的实际设计问题有所缓解。它充当了一个多路复用器以提供嵌套寻址。它将在总线阻塞于低电平时使其断接。它把一根很大的容性总线分裂成较小的分支,并允许I/O板卡在带电系统上进行热插拔。它可记录故障、向主控器报告、并与主控器一道高效地解决故障。

随着数据处理、海量存储和通信系统的发展,用于传送诸如温度、扇速、系统电压和关键产品数据(VPD,例如:电路板标识)等信息的子系统尺寸和复杂程度成比例地增长。在这些信息的传送中,最常用的就是两线式串行总线,比如:I2C或SMBus。

在这些系统的设计中会出现若干实际问题,特别在系统规模日益扩大的情况下更是如此。首先,诸如小型可插拔式光学模块(SFP)等众多设备都具有硬连线I2C地址,故由于地址冲突的原因而无法使用多个这样的设备。其次,由于设备种类的增加以及有越来越多的I/O板卡需要在系统上进行热插拔,因此,I2C设备产生混乱并把总线保持于低电平的可能性有所增加。第三,随着等效总线电容的增加,总线定时规格的满足变得困难起来。除了这些大的系统问题之外,在安装一个新的I/O板卡时进行功率循环并不是任何规格的不间断电源都拥有的功能选项。

具有总线缓冲器的LTC4306四通道两线式总线多路复用器/开关解决了所有这些问题。上行两线式总线(SDAIN、SCLIN)上的一个主控器可通过LTC4306的总线缓冲器和多路复用器/开关连接至下行总线的任何组合。因此,相同的设备地址可在多根下行总线上使用。缓冲器在上行和下行总线之间提供了容性隔离,从而为系统负载的分割创造了条件。上升时间加速器在克服电容局限性方面起到了进一步的帮助作用。当总线处于低电平的持续时间达到了设定的长度时,阻塞低电平超时电路将使上行总线与下行总线断接,从而把上行总线解放出来,以恢复通信。最后,LTC4306的任何两线式总线引脚都可在一个带电系统上进行插拔操作,而不会对其造成损害。LTC4306可采用2.7V至5.5V的电源电压。

一般操作

图1示出了LTC4306的方框图。UVLO比较器将阻止LTC4306接收命令,直到VCC电压升至2.5V(典型值)以上为止。这将确保LTC4306在其拥有足够的偏置电压之前不会试图运行。当ENABLE引脚被拉至1V以下时,LTC4306将被复位至其缺省的高阻抗状态,并且毫不理会在其两线式总线上进行的任何通信尝试。当ENABLE引脚被回拉至1.1V以上时,主控器可以恢复与LTC4306的通信。

与一根阻塞总线断接

当两线式总线阻塞于低电平的持续时间达到了一个设定的长度时,LTC4306将使上行总线与下行总线断接。主控器随后处于空闲状态,以在上行总线上恢复通信(假定问题的起因存在于一根下行总线上)。阻塞低电平超时电路负责监视下行SDA和SCL开关的两个共用的内部节点,并在任一个内部节点电压低于0.52V的情况下运行一个定时器。当这两个内部电压均高于0.6V时,该定时器将被复位。利用寄存器2,主控器能够设定7.5ms、15ms或30ms的时间,或者,它们也可选择停用超时功能。

两线式总线缓冲器和多路复用器开关提供了电容缓冲和电平移动

主控器向寄存器3写入数据,以连接至下行通道的任何组合。两线式总线缓冲器在上行SDAIN、SCLIN总线和下行总线之间提供容性隔离。由于拥有了此项功能,主控器便可在其系统的不同位置上采用LTC4306,以把一根大型总线分裂成若干个较小的总线。当连接了任何下行总线时,LTC4306将允许通过一个外部电阻器把READY引脚拉至一个逻辑高电平。

按照缺省设置,LTC4306仅与高电平的下行总线相连。与低电平下行总线相连的尝试将是劳而无功的,并将导致LTC4306把ALERT#引脚拉至低电平,以表示发生了一个故障。主控器可通过向寄存器2写入数据并指示LTC4306执行连接命令(这与下行总线的逻辑状态无关)来取代该功能。

上行和下行总线上拉电源电压可在2.2V至5.5V的范围内变化,而不受LTC4306 VCC电压的影响—— LTC4306因而能够在具有不同上拉电压的总线之间提供电平移动。为了保证同时连接多个下行通道时的正确运作,需确定LTC4306 VCC电压低于或等于所有的下行上拉电压,以维持逻辑高电平期间的通道至通道隔离度。

上升时间加速器缩短了上升时间

通过向寄存器2写入数据,主控器便可以起动或不起动上行总线和下行总线上的上升时间加速器。当起动时,加速器以一种受控方式接通,并向总线输送电流,以使它们在正总线转换期间以一个100V/μs的典型速率上升。这些大上拉电流使得用户能够在仍旧满足上升时间规格的同时构建庞大的重容性系统,但也进行了转换限制,以驱动长电缆。此外,由于加速器提供了强驱动,系统设计师因而能够选择大上拉电阻器来最大限度地减小总线逻辑低电压,由此实现逻辑低噪声容限的最小化。

故障信息为诊断提供了帮助

在发生了一个故障且LTC4306把ALERT#引脚拉至低电平之后,LTC4306将和主控器一道工作,以简单而迅速地解决故障。LTC4306把特定的故障信息存储于只读寄存器0之中。被存储的故障包括低电平阻塞总线、下行总线上的故障以及与一个下行通道的失败连接尝试。

如果故障的起因存在一根连接下行总线之上,则主控器可直接与出错器件进行通信。在这种场合,LTC4306以透明的方式运作,且主控器和出错器件通过LTC4306的总线缓冲器直接通信。

在所有其他的场合中,LTC4306与上行两线式总线上的主控器进行通信,以解决故障。在主控器发送了报警响应地址(ARA)之后,LTC4306利用其位于SDAIN上的地址做出响应,并释放ALERT#。如果由主控器来对其进行寻址,则LTC4306也将释放ALERT#。主控器通过读出寄存器0的内容来确定故障的起因。在主控器解决了问题之后,它把一个空字节写入寄存器0(这是一个只读寄存器),以使故障检测电路复位。

嵌套寻址和电平移动

图2所示电路示出了LTC4306的嵌套寻址、电平移动和电容缓冲功能。为简单起见,图中仅给出了通道1和4。请注意,背板、板卡1和板卡4被上拉至三个不同的电源电压。另外,虽然SFP模块具有相同的地址,但是,只要通道1和4决不同时运行,就不会发生地址冲突。

LTC4306位于背板之上时的两线式总线热插拔

图3示出了一个把LTC4306布设于背板之上并将一个I/O板卡插入下行通道4之中的电路。同样,为简单起见略去了通道2和3。在进行板卡插拔操作之前,需确定通道4未与上行总线相连,这样上行总线上发生的任何事务处理都不会受到干扰。如图所示,SDA4和SCL4上的上拉电阻器位于背板上,不过它们也可以安放在I/O板卡上,只要背板上的主控器在没有板卡插入时不与通道4相连即可。ALERT4#上的上拉电阻器必须设置在背板上,以防止在未插入板卡时发生错误的故障报告。

LTC4306位于I/O板卡之上时的两线式总线热插拔

在图4中,LTC4306位于具有4根单独下行总线的I/O板卡的边缘。把一个200kΩ电阻器从ENABLE引脚连接至地,并使ENABLE成为连接器上最短的引脚。这将确保ENABLE引脚在所有其他引脚均连接的情况下保持在一个恒定的逻辑低电平,因此,LTC4306将处于其缺省的高阻抗状态,且不会受到在连接期间SDAIN和SCLIN上连接瞬变的影响。此外,应使ALERT# 连接器引脚比VCC引脚短,这样,VCC就将在ALERT# 形成连接之前建立起与I/O板卡上拉电源引脚的可靠连接,并向ALERT1# ~ ALERT4#上的上拉电阻器供电。当断接时,ENABLE首先断开连接,并使LTC4306复位至其缺省状态,因而当板卡断接时其在SDAIN和SCLIN总线上引起的扰动极小。

结语

LTC4306使得与大型两线式总线系统相关的实际设计问题有所缓解。它充当了一个多路复用器以提供嵌套寻址。它将在总线阻塞于低电平时使其断接。它把一根很大的容性总线分裂成较小的分支,并允许I/O板卡在带电系统上进行热插拔。它可记录故障、向主控器报告、并与主控器一道高效地解决故障。