- 易迪拓培训,专注于微波、射频、天线设计工程师的培养

基于LPC2294的CAN总线主节点设计

摘要:为引入CAN总线技术以实现运动控制系统的网络化。提出了基于LPC2294的CAN总线主节点的硬件及软件设计方案。硬件采用基于ARM7内核的微控制器LPC2294,使用CTM1050T作为CAN收发器,设计了带有CAN总线以及以太网接口的硬件电路,并进行了SRAM、NORFLASH与NAND Flash的扩展。软件采用μCLinux作为操作系统,并开发了CAN控制器的驱动程序,实现了CAN总线的各种功能。通过制作样机并进行实验,验证了这一方案的有效性。

CAN(Controller Area Network)即控制器局域网络,是国际上应用最广泛的现场总线之一,已经成为计算机控制系统和嵌入式工业控制局域网的标准总线。网络化运动控制系统(Networked Motion Control Systems)就是构建在控制器与电机驱动器之间,能够实时、同步地传送运动控制指令和接收运动状态,并且控制闭环通过网络连接的运动控制系统。为引入CAN总线技术以实现运动控制系统的网络化,笔者提出一种基于LPC2294的CAN总线主控制节点的硬件及软件设计方案,具有高性能、高可靠及良好扩展性的特点,非常适用于运动控制系统。

1 总体设计

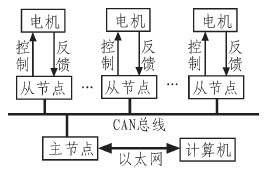

主节点采用ARM7内核的LPC2294微控制器,使用RTL8019AS作为以太网控制器,软件上采用具有网络功能强、性能稳定、移植性好的μCLi nux作为操作系统。基于CAN总线的运动控制系统,主要由1个主节点(主控制器节点)、若干个从节点(电机控制节点)以及1台计算机构成,主节点与从节点之间通过CAN总线进行通信,主节点与计算机之间则通过以太网进行通信,如图1所示。

图1 运动系统控制结构

主节点主要功能包括:1)通过CAN总线发送电机控制信息给从节点,并接收各从节点的反馈信息:2)通过以太网与计算机监控端进行通信,以实现远程监控。

1.1 整体硬件设计

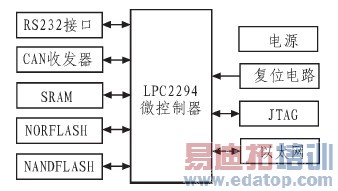

主节点整体硬件结构如图2所示。

图2 硬件结构

主节点采用的LPC2294基于ARM7TDMI内核的32位处理器,带有256kB高速FLASH、16kB静态RAM,内部集成4路CAN控制器,支持SRAM、FALSH扩展。由于LPC2294内部集成CAN,因此外部只需CAN收发器与之连接。CAN收发器选用周立功的CTMl050T。CTM1050T是一款带隔离的高速CAN收发器,主要功能是将CAN控制器的逻辑电平转换为CAN总线的差分电平,并具有隔离功能(DC2500V)、ESD保护功能及TVS管防总线过压功能。LPC2294具有外部存储器控制器(EMC),通过该部件可以扩展更多的FLASH和SRAM以及以太网、USB等外设。主节点采用RTL8019AS作为以太网控制器,分别使用MT45W4MW16、SST39VF1601、K9F2G08UOA进行SRAM、NORFLASH、NANDFLASH的扩展。

1.2 软件结构

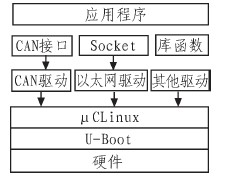

主节点软件结构如图3所示,U-Boot作为BootLoader(启动引导程序),负责初始化目标板硬件与引导操作系统。这里采用μCLinux作为嵌入式操作系统。μCLinux(microcontrol linux)即"微控制器领域中的Linux系统",主要是针对目标处理器没有存储管理单元(MMU)的嵌入式系统而设计的。它保留了Linux的大多数优点:稳定、良好的移植性、优秀的网络功能、对各种文件系统完备的支持和标准丰富的API。同时μCLinux包含大量的设备驱动程序,以及提供良好的驱动程序开发框架。驱动程序开发或配置主要包括CAN、以太网以及NANDFLASH3大部分。上层应用程序通过使用CAN接口函数、Socket接口以及库函数进行各种应用开发。整个系统的启动过程是:U-Boot把μCLinux内核从NORFLASH中加载到SRAM中,然后启动μCLinux,μCLinux初始化硬件及建立运行环境后,自动运行预设的应用程序。

图3 软件结构

2 硬件设计

2.1 LPC2294最小系统

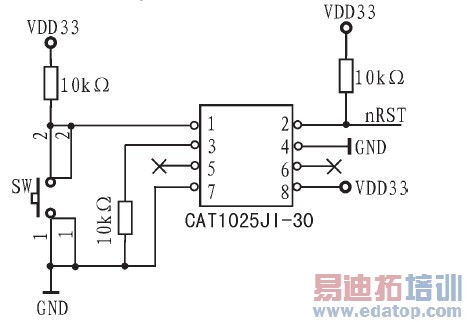

LPC2294采用LQFP144封装,最小系统需要模拟和数字3.3V电源以及核心电源1.8V。为了便于串口波特率的设置,外部接11.0592MHz晶振。P2.26(BOOT0)通过10kΩ电阻上拉,P2.27(BOOT1)接一跳线座,通过跳线让P2.27可选择接高电平或低电平以选择从内部FLASH或外部NORFLASH启动。由CAT1025构成手动复位监控电路,提高了系统的可靠性。当SW按键按下时,CAT1025的2引脚输出持续为大于150ms的低电平,LPC2294复位。在CAT1025的2引脚通过10kΩ电阻上拉,防止产生错误的引脚输出状态,复位电路如图4所示。

图4 复位电路图

2.2 SRAM和NORFLASH电路

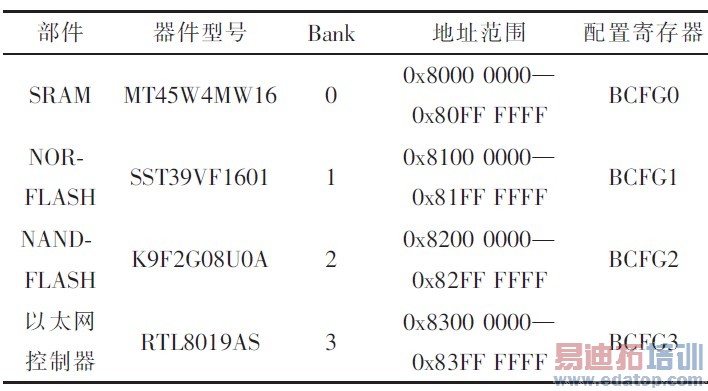

为了运行μCLinux操作系统,必须扩展系统RAM与FLASH。LPC2294具有外部存储器控制器(EMC),该部件可同时支持多达4个单独配置的存储器组。每个存储器组都支持SRAM、ROM、Flash EPROM、Burst ROM以及外部I/O设备。主节点外部存储器地址分配情况如表1。

表1 主节点外部存储器地址分配情况

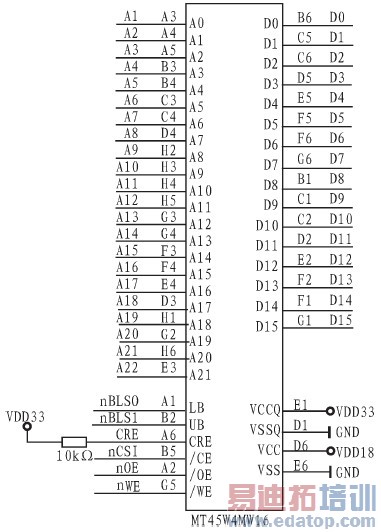

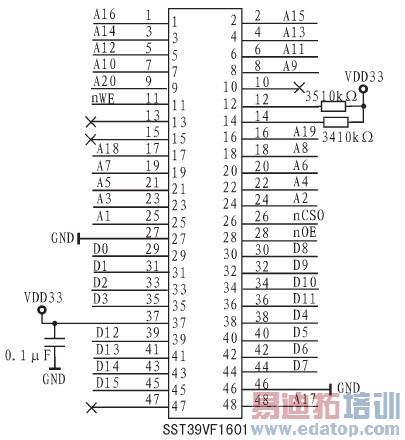

主节点采用的SRAM和NORFLASH分别是MT45W4MW16、SST39VF1601。MT45W4MW16是一个16位、8MB容量的PSRAM。SST39VF1601是一个16位的CMOS多功能Flash MPF器件,储存容量为2MB。其电路连接如图5、图6所示。

图5 SRAM电路连接图

图6 NORFLASH电路连接图

2.3 NANDFLASH电路

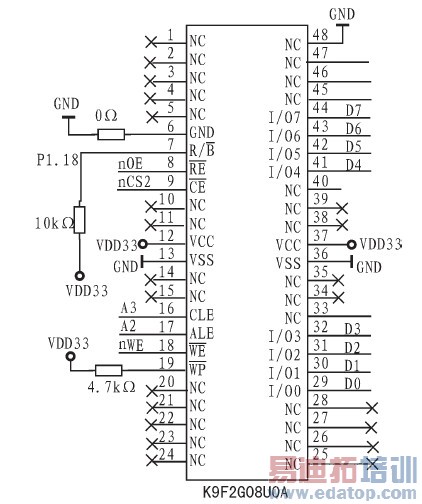

NANDFLASH用作存放μCLinux的根文件系统和应用程序,使用Jff2文件系统格式。NANDFLASH采用三星公司的K9F2G08UOA,存储容量为256M。NANDFLASH的数据接口为8位串行接口,使用nCS2作为片选线,地址区间使用0x8200 0000-0x82FF FFFF,CLE(指令使能)和ALE(地址使能)分别连接到地址总线A2和A3,因此NANDFLASH的数据写入地址为0x82000000,命令写入地址为0x82000004,地址写入地址为0x82000008.R/B(准备/忙等待)连接到P1.18,用于读取当前状态,此引脚须上拉。其电路连接如图7所示。

图7 NANDFLASH电路连接图

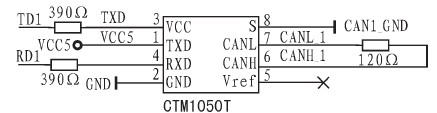

2.4 CAN接口电路

LPC2294内部集成了4路CAN控制器。每个总线上的数据传输速率高达1Mb/s,兼容CAN2.0B。LPC2294没有集成CAN收发器,无法将TTL电平转换为CAN总线的差分电平信号。因此主节点采用了带有隔离功能的CTM1050T作为CAN收发器。在CAN总线两端须连接120Ω的电阻,以匹配总线阻抗,提高数据通信的抗干扰性及可靠性。以下是1路CAN收发器的电路图,其余3路连接方式与此一样。

图8 CAN收发器电路图

2.5 以太网电路

主节点采用RTL8019AS作为以太网控制器。RTL8019AS是一种全双工即插即用的以太网控制器,已集成了RTL8019内核和一个16kB的SDRAM存储器。它兼容RTL8019控制软件和NE2000 8bit或16 bit的传输。网络接口采用带网络变压器的HR901170A。RTL8019AS使用的片选线为nCS3,地址范围为0x8300 0000-0x83FF FFFF,由于只有256B的寄存器,因此可操作地址范围为0x8300 0000-0x8300 00FF。RTL8019AS使用20M晶振。

3 软件设计

3.1 U-Boot移植

U-Boot(Universal Boot Loader)是遵循GPL条款的开放源码项目。从FADSROM、8xxROM、PPCBOOT逐步发展演化而来,支持多种嵌入式操作系统内核与微处理器系列。U-Boot的启动过程:初始化目标板硬件。给嵌入式操作系统提供板上硬件资源信息,加载、引导嵌入式操作系统。主节点使用U-Boot-2009-01,它不仅支持ARM-720T内核,而且间接提供了对LPC2294的板级支持。U-Boot的移植过程:首先通过修改star t.s文件设定系统主频:然后针对U-Boot所支持的LPC2292硬件资源配置信息作必要的修改,如外部存储器控制器(EMC)、以太网控制器等的硬件连接信息;接下来修改串口驱动代码使之与系统主频匹配;最后通过配置菜单配置U-Boot,主要配置所需要的命令和所要支持的硬件。

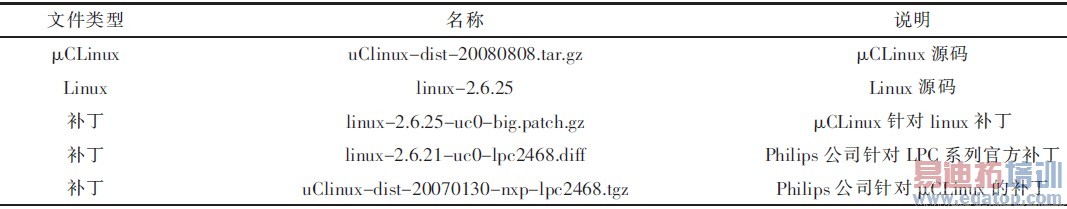

3.2 μCLinux移植

LPC2294没有MMU单元,不能运行定制的Linux,只能使用μCLinux。主节点移植的μCLinux版本号为2.6.25。从该版本开始,μCLinux支持CAN总线驱动。移植过程如下:

1)打Philips公司针对该芯片提供的官方补丁;

2)修改NANDFLASH部分的驱动程序;

3)配置μCLinux内核;

4)交叉编译内核。

所需源码及补丁文件如表2所示。

表2 所需源码及补丁文件

移植需要修改的部分驱动代码:

1)修改arch/arm/math-lpc22xx/head.s

因为μCLinux假设运行前已由BootLoader完成基本硬件初始化工作,因此不再进行系统时钟频率、串口初始化等基本硬件的初始化。在head.s文件中包括初始化存储器控制器、系统分频器PLL等部分代码,需要更改这部分代码,使之与U-Boot中Lowlevel_init.s文件的描述一致。另外μCLinux运行前必须由BootLoader将其内核装入内存偏移量为0x80000000的地方,因此要保证在μCLinux源码中的对应设置与启动引导程序的初始化设置相同。

2)修改NANDFLASH驱动代码

μCLinux内核从2.6.14开始更改了NANDFLASH的驱动代码,使驱动更加智能化,不再需要写读写函数,只需要实现读写时序函数。时序函数只关心如何来发送指令到NANDFLASH,例如写指令周期需要对ALE线使能,那么μCLinux下的读写函数会给这个时序函数发送一段指令中包含使能ALE线的指令,然后将数据写到数据总线上,CLE的实现与之相类似。

3.3 CAN控制器驱动设计

对于微处理器来说,CAN控制器完全是基于事件触发的,即CAN控制器会在本身状态发生改变时,会将状态变化的结果告诉微处理器。所以微处理器处理CAN控制器时,可以采用中断的方式,也可以采用轮询查看CAN控制器状态的方式来对CAN控制器做出相应的处理。在μCLinux下CAN驱动程序设计包括初始化函数、读函数、写函数、中断服务函数等设计,使用文件指针注册设备,用户程序则通过对设备文件的操作来收发CAN总线数据。CAN驱动程序主要功能包括:

1)CAN控制器的初始化CAN控制器的初始化工作包括硬件使能CAN、设置管脚连接、软件复位、设置CAN报警界限、设置总线波特率、设置中断工作方式、设置CAN验收过滤器的工作方式以及启动等。

2)CAN总线数据发送先将数据送到发送缓冲区,然后对发送寄存器赋值以启动发送。CAN控制器只负责发送,并不保证发送成功。因此要知道是否发送成功,须查询TCS状态位,或配合发送成功中断来判断。

3)CAN总线数据接收CAN总线数据接收通过读取状态寄存器查询当前缓冲区中是否有数据,当有数据时将数据读出并放到CAN接收环形数据存储区中,当用户程序需要数据时则从该缓存区中读出。

4)CAN中断处理通过中断获知CAN控制器的当前状态,然后做出相应的处理,包括接收中断处理、发送中断处理以及异常中断处理。中断处理由中断服务函数实现。

4 结论

本文提出一种基于LPC2294微控制器,使用μCLinux作为操作系统的CAN主节点软硬件设计方案。主节点通过扩展SRAM、FLASH提高了系统的性能,采用带隔离功能的CAN收发器增强了CAN总线节点的抗干扰能力,外接以太网控制器实现了计算机远程监控。基于μCLinux的软件系统既提高了系统的稳定性、应用软件的开发效率,又使得众多的Linux平台软件可容易地移植到主节点,增强系统的功能。通过制作了样机并进行实验,验证了这一方案的有效性。

作者:黄培灿 赵维佺 黄荣舜 邹裕 来源:《电子设计工程》2011年12期